JESD204C IP

Filter

Compare

27

IP

from

9

vendors

(1

-

10)

-

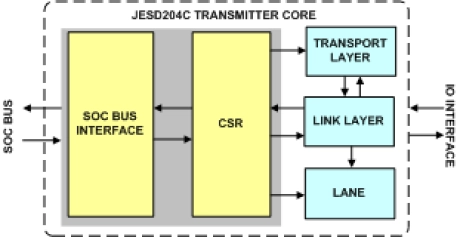

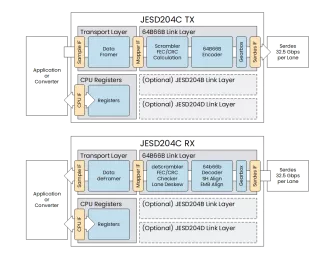

JESD204C Transmitter IIP

- Compliant with JESD204 specification JESD204A, JESD204B.01 and JESD204C.

- Full JESD204C transmit functionality.

- Supports data rate upto 32 Gbps.

- Supports programmable clock frequency up to 32 GHz.

-

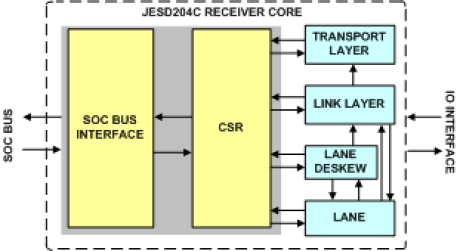

JESD204C Receiver IIP

- Compliant with JESD204 specification JESD204A, JESD204B.01 and JESD204C.

- Full JESD204C receive functionality.

- Supports data rate upto 32 Gbps.

- Supports programmable clock frequency up to 32 GHz.

-

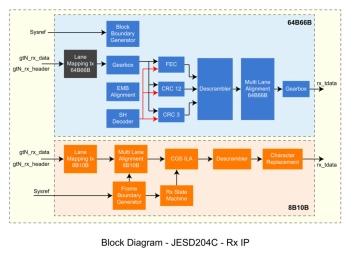

JESD204C Transmitter and Receiver

- With the addition of error correction and Detection(FEC, CRC), cutting-edge instrumentation and other applications can operate without any errors.

- Offers better DC balance, clock recovery and data alignment compared to JESD204B.

- The bit overhead is 3.125% which is much smaller than JESD204B (~ 25%).

- Provides interface for serializing devices from some system designs, reducing space, power, and cost.

-

JESD204C Controller IP

- Designed to JEDEC JESD204C.1 specification

- Line rates from 1 Gbps to 32.5 Gbps

- Supports 1-24 lanes

- Supports 1-96 converters

-

5G RedCap L1 modem IP

- 3GPP release 18

- 220Mbps/120Mbps DL/UL throughput

- LTE Cat 4 fallback option

- 2Rx or 1Rx option

-

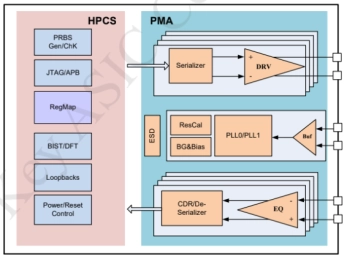

Single-carrier RF transceiver on TSMC 22nm ULL

- TSMC 22nm Ultra Low Leakage

- 1Tx/1Rx, 1Tx/2Rx, 2Tx/2Rx options

- 450-5000MHz

- Up to 20MHz bandwidth

-

Multi-carrier RF transceiver on TSMC 22nm ULL

- TSMC 22nm Ultra Low Leakage

- Up to 10 synthesizers

- Up to 4Tx/20Rx

- 220-7125MHz

-

-

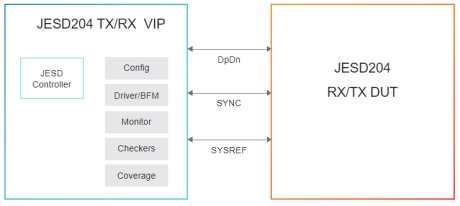

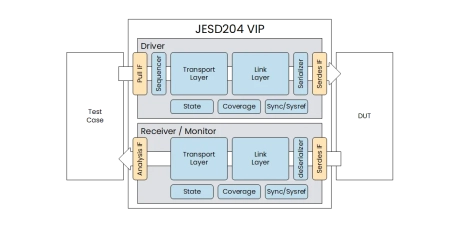

JESD204 Verification IP

- This JESD204 Verification IP provides an advanced and efficient solution for verifying and debugging these standards in a UVM simulation environment.

- The verification IP helps reduce time to test, accelerate verification process and ensures a high quality for the end-product.

-

Simulation VIP for JESD204

- Topology

- Transmitter or receiver configuration

- Clock Frequency

- Any frequency is supported, as the VIP works on the source clock