HBM2 IP

Filter

Compare

36

IP

from

10

vendors

(1

-

10)

-

HBM2E and HBM2 FPGA IP

- HBM2E and HBM2 are high-performance memory IPs that offer a combination of high memory bandwidth, low power consumption, low latency, and small form factor for Agilex™ 7 FPGA M-Series and Stratix® 10 MX FPGAs, respectively

- HBM2E and HBM2 are well-suited for a variety of high-performance computing applications.

-

HBM2 Controller IIP

- Supports HBM2 protocol standard JESD235 and JESD235A Specification

- Compliant with DFI version 4.0 or 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

HBM2 Memory Controller

- Support Pseudo Channel mode with 64DQ per Pseudo Channel

- Support DFI1:1

- Support HBM Burst Length 4

- Support 4 High or 8 High HBM Devices

-

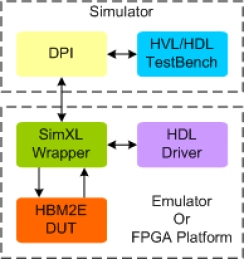

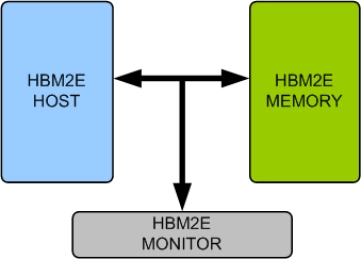

HBM2E Synthesizable Transactor

- Supports 100% of HBM2E protocol standard JESD235B,JESD235C and JESD235D.

- Supports all the HBM2E commands as per the specs

- Supports all types of timing and protocol violation detection

- Supports burst length of 2 and 4

-

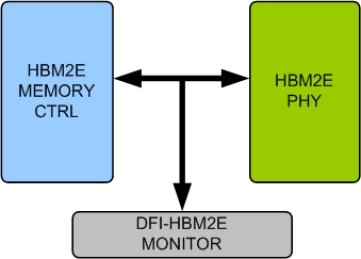

HBM2E DFI Synthesizable Transactor

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports HBM2E devices compliant with JEDEC HBM2E DRAM Standard JESD235B and JESD235C.

- Supports all Interface Groups.

- Supports Write Transactions with Data mask

-

HBM2E Memory Model

- Supports HBM2E memory devices from all leading vendors.

- Supports 100% of HBM2E protocol standard specification JESD235B,JESD235C and JESD235D.

- Supports all the HBM2E commands as per the specs.

- Supports programmable clock frequency of operation.

-

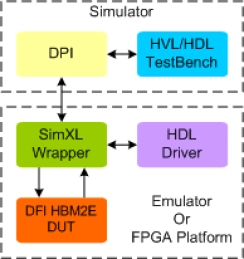

HBM2E DFI Verification IP

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports HBM2E devices compliant with JEDEC HBM2E DRAM Standard JESD235B and JESD235C.

- Supports all Interface Groups.

- Supports Write Transactions with Data mask

-

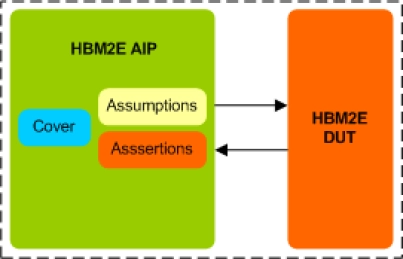

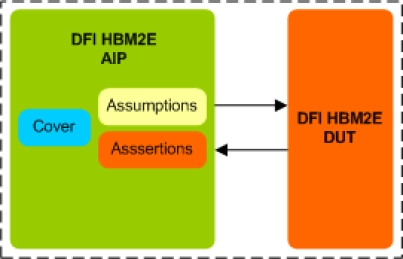

HBM2E DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports HBM2E devices compliant with JEDEC HBM2E DRAM Standard JESD235B and JESD235C.

- Supports all Interface Groups.

-

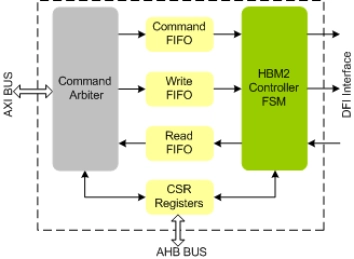

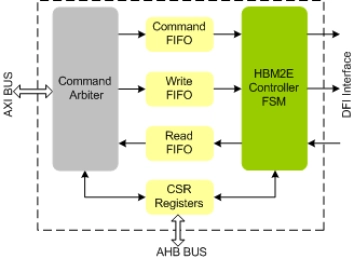

HBM2E Controller IIP

- Supports HBM2E protocol standard JESD235B and JESD235C with revision 4.10 Specification.

- Compliant with DFI version 4.0 or 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels.

-

HBM2E Assertion IP

- Specification Compliance

- Supports HBM2E memory devices from all leading vendors.

- Supports 100% of HBM2E protocol standard specification JESD235B,JESD235C and JESD235D.

- Supports all the HBM2E commands as per the specs.