FEC and IP

Filter

Compare

252

IP

from

51

vendors

(1

-

10)

-

Generic Polar FEC Encoder and Decoder

- Fully-pipelined architecture

- Support for systematic and non-systematic encoding

- Support for coded block lengths of up to 1024 bits

- Support for a wide variety of

-

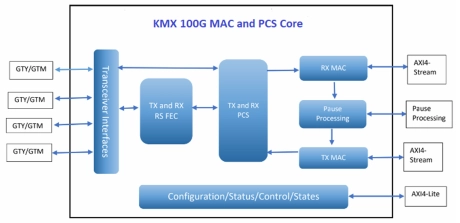

100G MAC and PCS core

- KMX 100G MAC and PCS core, which consists of media access control (MAC) module, physical coding sublayer (PCS) module and physical medium attachment (PMA) module, is compliant with the IEEE 802.3ba-2010 standard.

- The core implements RS FEC as defined in IEEE 802.3bj Clause 91 with independent bit error detection and bit error correction.

-

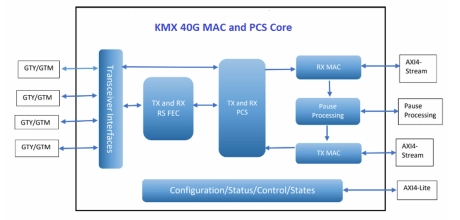

40G MAC and PCS core

- KMX 40G MAC and PCS core, which including media access control (MAC) module, physical coding sublayer (PCS) module and physical medium attachment (PMA) module, is compliant with the IEEE 802.3ba-2010 standard.

- The core supports RS FEC as defined in Clause 74 IEEE 802.3 with independent error bit detection and error bit correction.

-

224G SerDes PHY and controller for UALink for AI systems

- UALink, the standard for AI accelerator interconnects, facilitates this scalability by providing low-latency, high-bandwidth communication.

- As a member of the UALink Consortium, Cadence offers verified UALink IP subsystems, including controllers and silicon-proven PHYs, optimized for robust performance in both short and long-reach applications and delivering industry-leading power, performance, and area (PPA).

-

oFEC Encoder and Decoder

- OpenROADM oFEC (Open Forward Error Correction) is a core element of the OpenROADM initiative, providing a standardized, open-source FEC solution for high-speed coherent optical networks.

- The oFEC IP cores deliver high coding gain through a fully parallel, pipelined decoder architecture with 3 soft-decision (SD) and 2 hard-decision (HD) decoding steps. It supports data rates from 200G to 800G, including Probabilistic Constellation Shaping (PCS) modes to enhance spectral efficiency, noise tolerance, and transmission reach.

-

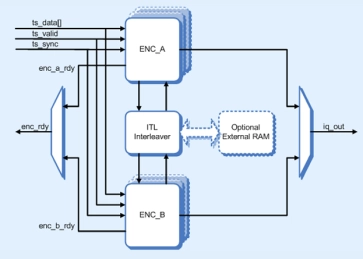

Multi-channel DVB-C / J83 FEC encoder

- The CMS0044 J.83abc/DVB-C Cable FEC Encoder combines all of the channel coding and Forward Error Correction functions specified by DVB-C and by J83 Annexes A B and C.

- It is designed to interface to external modulators or advanced upconverting DACs such as the Analog Devices AD9789.

-

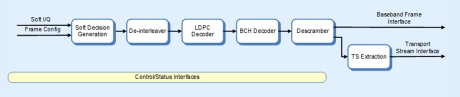

DVB-Satellite FEC Decoder

- The CMS0077 Satellite FEC Decoder has been designed specifically to meet the requirements of the DVB-S2 and DVB-S2X advanced wide-band digital satellite standards.

- The core provides all the necessary processing steps to convert a demodulated complex I/Q signal into a standard TS output stream.

-

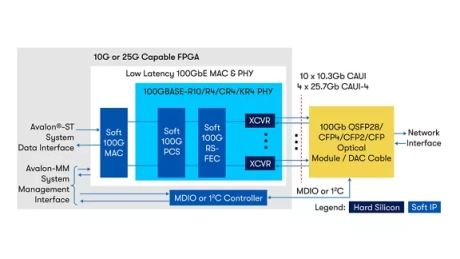

Low Latency Ethernet 100G MAC and PHY Intel® FPGA IP Core

- Intel® offers ultimate flexibility, scalability, and configurability with the Low Latency 100G Ethernet Intel® FPGA IP core targeted to network infrastructure and data centers.

- The Low Latency 100G Ethernet Intel® FPGA IP core is compliant with the IEEE 802.3ba-2010 standard, it includes a media access control (MAC), PHY, physical coding sublayer (PCS), physical medium attachment (PMA), and an optional forward error correction (FEC) block.

- It also includes IEEE 1588v2 timestamping support and the capability to drive backplanes on supported Intel® Stratix® and Intel® Arria® FPGAs. This IP can be used for chip-to-chip interfaces using copper interconnect or optical transceiver modules

-

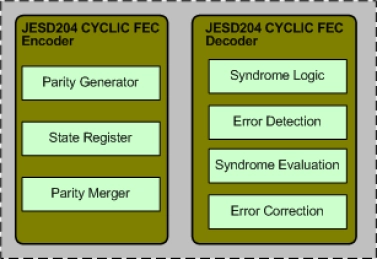

JESD204 CYCLIC FEC IIP

- Compliant with JESD204 specification JESD204C.

- Supports Full JESD204C FEC functionality.

- This FEC(Forward Error correction) methodology implements the (2074, 2048) binary cyclic code is shortened from the cyclic Fire code (8687, 8661).

- Supports FEC of 26 bits parity bits.

-

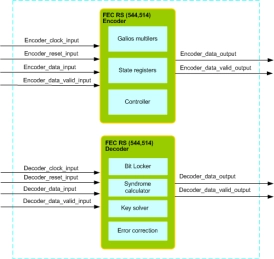

FEC RS (544,514) IIP

- Compliant with CPRI Specification V7.0, IEEE Standard 802.3.2018 Ethernet specification and JESD204D Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (544,514) FEC, 10-bit symbols.

- Supports different input and output data widths of multiples of 10-bits.