Digital Blocks IP

Filter

Compare

288

IP

from

53

vendors

(1

-

10)

-

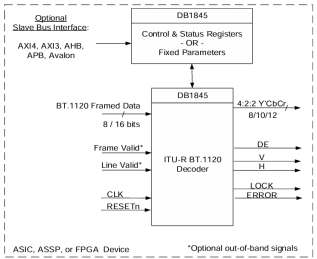

ITU-R BT.1120 Decoder – HD 1920x1080p

- The DB1845 ITU-R BT.1120 / BT.656 Decoder IP Core decodes ITU-R BT.1120 and BT.656 digital video uncompressed NTSC and PAL video, extracting Y’CbCr 4:2:2 video components and frame timing & status signals.

-

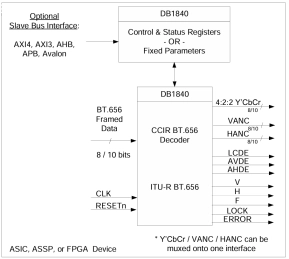

ITU-R BT.656 Decoder

- The DB1840 CCIR 656 Decoder IP Core decodes an ITU-R BT.656 digital video uncompressed NTSC 720x486 (525/60 Video System) and PAL 720x576 (625/50 Video System) Standard Definition frame, extracting Y’CbCr 4:2:2 video components, optional Ancillary Data, and frame timing & status signals.

-

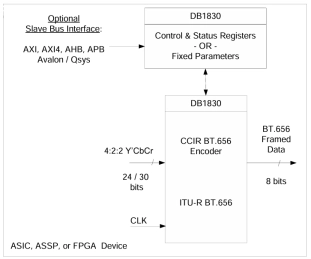

ITU-R BT.656 Encoder

- The DB1830 CCIR 656 Encoder IP Core encodes 4:2:2 Y’CbCr component digital video with synchronization signals to conform to NTSC & PAL video ITU-R BT.656 digital coding standard.

-

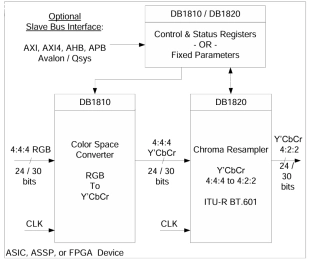

Color Space converter & Chroma Resampler- 4:4:4 RGB to 4:2:2 Y’CbCr

- The DB1825 Color Space Converter & Chroma Resampler Verilog IP Core transforms 4:4:4 sampled RGB color components to 4:4:4 Y’CbCr color space followed by Chroma Resampling to 4:2:2 sampled Y’CbCr color components.

-

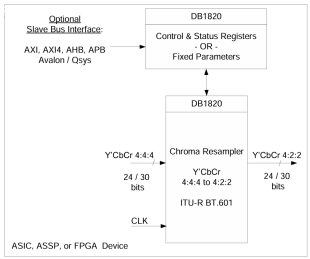

4:4:4 Y’CbCr to 4:2:2 Y’CbCr Chroma Resampler (ITU-R BT.601)

- The DB1820 Chroma Resampler IP Core down converts 4:4:4 Y’CbCr to 4:2:2 Y’CbCr in accordance with the ITU-R BT.601 standard requirements.

-

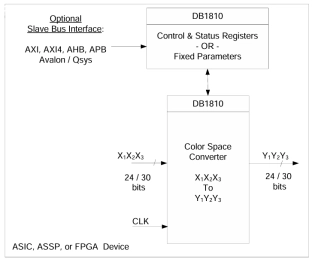

Color Space Converter

- The DB1810 Color Space Converter IP Core transforms three color components from one color space to another. An image can be sourced in one color space, while more efficiently processed, stored, or transmitted in another space, while still more effectively displayed in a third color space.

-

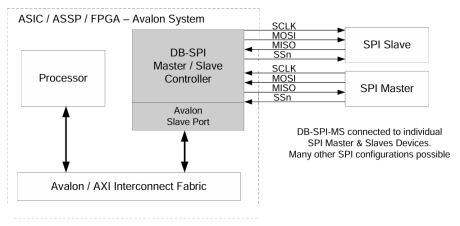

SPI Controller IP- Master/ Slave, Parameterized FIFO, Avalon Bus

- The Digital Blocks DB-SPI-MS-AVLN is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting both Master/Slave SPI Bus transfers.

- The DB-SPI-MS contains an Avalon Bus Interface for interfacing a microprocessor to external SPI Master/Slave devices.

-

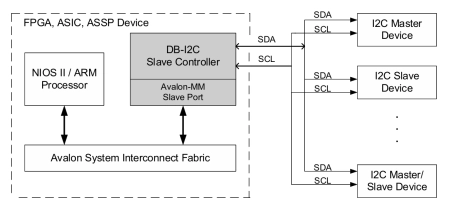

I2C Controller IP – Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-S-AHB Controller IP Core interfaces a NIOS II, ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the Avalon System Interconnect Fabric to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

-

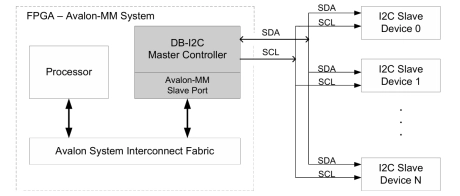

I2C Controller IP – Master, Parameterized FIFO, Avalon Bus

- The DB-I2C-M-AVLN Controller IP Core interfaces a microprocessor via the Avalon Bus to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

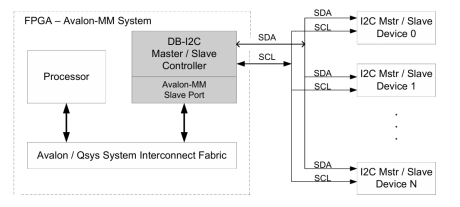

- The DB-I2C-M-AVLN is a Master I2C Controller that controls the Transmit or Receive of data to or from slave I2C devices. In an Altera FPGA, typically, the microprocessor is a NIOS II processor, but can be any FPGA embedded processor. Figure 1 depicts the system view of the DB-I2C-M-AVLN Controller IP Core embedded within an FPGA integrated circuit device.

-

I2C Controller IP- Master / Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-MS-AVLN Controller IP Core interfaces a microprocessor via the Avalon Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-MS-AVLN is a Master / Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.