DDC IP

Filter

Compare

62

IP

from

14

vendors

(1

-

10)

-

-

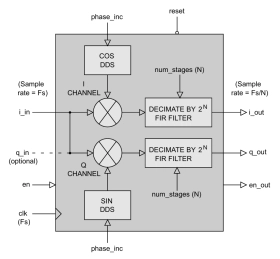

Wideband DDC

- Contains Numerical Controlled Oscillators, IF mixers, decimator, and halfband filters.

- High input throughput of up to 2.4 Gsps.

- Supported signal bandwidth of up to 600 MHz.

- Tunable IF frequency from 10 to 700 MHz with a precision of at least 2 Hz.

-

Wideband Digital Down Converter (Digital DDC)

- Fully synchronous design, using single clock

- Fully synthesizable drop-in module for FPGAs

- Optimized for high performance and low resources

- Low implementation loss

-

Digital Down Converter with configurable Decimation Filter

- 16-bit signed complex (IQ) data samples

- Precision digital oscillator (> 100 dB SFDR)

- Decimation factors from 0 to 2^N

- Only 12 multipliers per decimate-by-2 stage

-

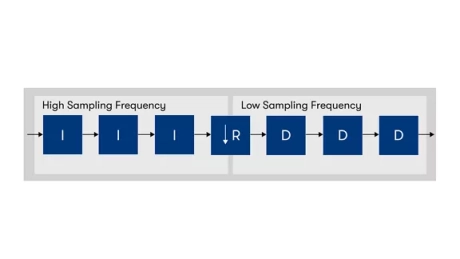

CIC Intel® FPGA IP Core

- The CIC Intel FPGA IP core implements a Cascaded integrator-comb (CIC) filter with data ports that are compatible with the Avalon® streaming (Avalon-ST) interface

- CIC filters (also known as Hogenauer filters) are computationally efficient for extracting baseband signals from narrow-band sources using decimation

- They also construct narrow-band signals from processed baseband signals using interpolation.

-

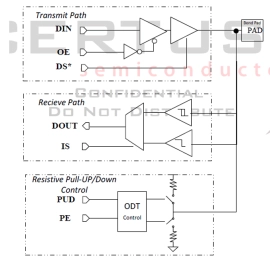

1.8V/3.3V I/O library with ODIO and 5V HPD in TSMC 16nm

- A 1.8V/3.3V flip-chip I/O library with 4kV HBM ESD protection, I2C compliant ODIO and Hot-Plug Detect.

- This library is a production-quality, silicon-proven I/O library in TSMC 16nm technology.

- Supports multi-voltage GPIOs, capable of operating at 1.8V or 3.3V, dynamically selectable at the system level.

-

1.8V/3.3V I/O Library with ODIO and 5V HPD in TSMC 12nm

- A 1.8V/3.3V flip-chip I/O library with 4kV HBM ESD protection, I2C compliant ODIO and Hot-Plug Detect.

- This library is a production-quality, silicon-proven I/O library in TSMC 12nm technology.

- Supports multi-voltage GPIOs, capable of operating at 1.8V or 3.3V, dynamically selectable at the system level.

-

1.8V to 5V GPIO, 1.8V to 5V Analog in TSMC 180nm BCD

- A Flip-Chip compatible I/O Library in TSMC 180nm BCD with 1.8V to 5V GPIO, 1.8V to 5V analog, with ultra low-cap/low-leakage RF solutions.

- This silicon proven flip-chip compatible library in TSMC 180nm BCD features a multi-voltage GPIO, 1.8V to 5V analog I/O, and ultra-low capacitance and low leakage 36V+ ESD solutions. The library also includes 5V RF pads.

-

1.8V GPIO, 1.8V to 3.3V Analog in TSMC 180nm BCD

- A Flip-Chip compatible I/O Library in TSMC 180nm BCD with 1.8V GPIO, 1.8V to 3.3V Analog, with ultra low-cap/low-leakage 36V+ ESD solutions.

- This silicon proven flip-chip compatible library in TSMC 180nm BCD features a 1.8V GPIO, 1.8 to 3.3V analog I/O, and ultralow capacitance and low leakage 36V+ ESD solutions.

-

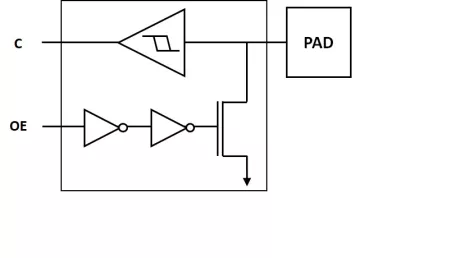

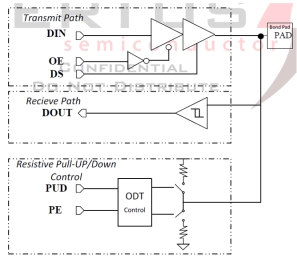

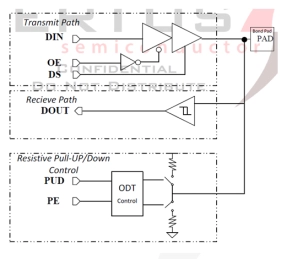

1.8V/3.3V Multi-Voltage GPIO in TSMC 28nm

- This silicon-proven TSMC 28nm Digital I/O Library delivers a high-performance, low-power interface solution designed for advanced digital applications.

- Featuring a triple-staggered architecture, this versatile library supports multi-voltage and multi-protocol GPIO, ensuring seamless integration across diverse system requirements.