BPSK IP

Filter

Compare

58

IP

from

23

vendors

(1

-

10)

-

Burst-mode BPSK Modem with highly efficient packet structure

- Fully synchronous design, using single clock

- Fully synthesizable drop-in module for FPGAs

- Optimized for high performance and low resources

- Low implementation loss

-

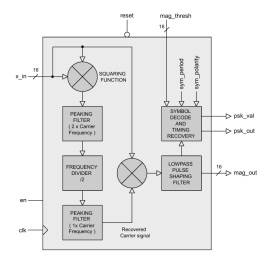

Binary-PSK Demodulator

- The BPSK_DEMOD IP Core is a 16-bit resolution Binary-PSK demodulator based on a multiply-filter-divide architecture.

- The design is robust and flexible and allows easy connectivity to an external ADC.

-

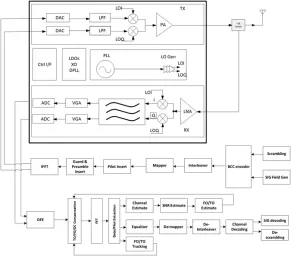

FH-OFDM Modem

- The FH-OFDM modem is developed for OFDM applications used in frequency hopping transmission scenarios or fixed frequency scenarios.

-

FH-OFDM Modem

- The FH-OFDM (multicarrier) modem is developed for OFDM applications used in frequency hopping transmission scenarios or fixed frequency scenarios.

- The modem mainly consists of two components. The first component is an FH modem that is used to establish communication during hopping and to synchronize the communication. Once established, data communication is then performed via the second component, which is an OFDM modem.

-

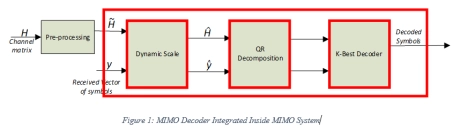

MIMO Decoder

- Includes QR Decomposition, Dynamic scale and K-best Decoder

- Fixed Depth K-Best Decoder (K=16)

- Achieves close-to ML BER performance

- Supports synchronized streams with different QAM (from BPSK to 64 QAM) dependent on MIMO mode

- Supports square and non-square QAM

-

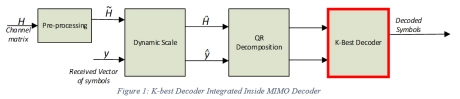

K-Best MIMO 3×3 Decoder

- Fixed Depth K-Best Decoder (K=16)

- Achieves close-to ML BER performance

- Supports three streams with different QAM (from BPSK to 64 QAM)

- Supports square and non-square QAM

- Supports OFDM based systems with different Space Time Coding (STC)

-

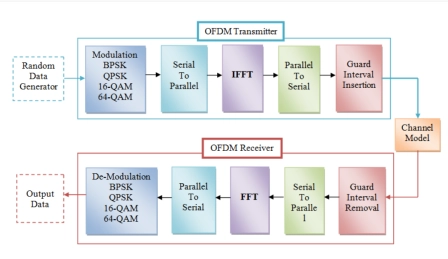

OFDM - Orthogonal Frequency Division Multiplexing

- Configure and create complete multiple OFDM Frames with Preamble, Header, and Payload

- Preset for Standard compliant Frames for various wireless standards like Wi-Fi, WiMAX

- Define Frame with Preamble, Header, and Payload (selectively) to simulate different OFDM signals

-

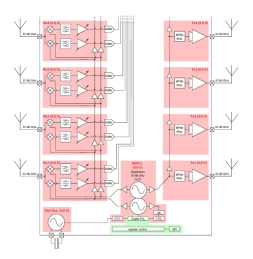

Ultra-low-power 60 GHz radar-on-chip

- CSEM has developed a low-cost, ultra-low-power 60 GHz MIMO FMCW PHY that can be integrated into radar-on-chips with custom digital processing for specific applications.

- This solution leverages CSEM’s decades of experience in ultra-low-power RF CMOS system-on-chip design.

-

802.11ah IP - GLOBALFOUNDRIES 22nm FDX

- Process Technology: GLOBALFOUNDRIES 22nmFDX

- Operation voltage: core 0.8v, I/O 1.8v

- Operation Band: 863MHz ~ 928MHz

- Power and clock blocks are integrated in IP

-

LDPC for 5G DVBS2 802.11

- High throughput

- One encoder and decoder per matrix

- Five cycles per iteration may increase to around 10 for timing between gates.

- Has configuration parameters for stopping if code is diverging.