BCH Encoder Decoder IP

Filter

Compare

12

IP

from

9

vendors

(1

-

10)

-

-

DVB-S2 LDPC BCH Decoder and Encoder

- The DVB-S2 LDPC-BCH block is a powerful FEC (Forward Error Correction) subsystem for Digital Video Broadcasting via Satellite.

- In Digital video broadcasting for digital transmission for satellite applications, a powerful FEC sub-system is needed. FEC is based on LDPC (Low Density Parity Check) codes concatenated with BCH (Bose Chaudhuri Hocquenghem) codes, allowing Quasi Error Free operation close to the Shannon limit.

-

BCH encoder and decoder for NAND FLASH

- Parameter customizable

- AXI interface, easy integration

- High throughput with low complexity hardware

-

DVB-S2 BCH and LDPC Encoder and Decoder

- Compliant with ETSI 302 307 V1.2.1 (2009-08) (DVB-S2).

- Support for short blocks (16200 bits) and long blocks (64800 bits).

- Support for all modulation schemes (QPSK, 8-PSK, 16-APSK, 32-APSK).

- Support for all interleaving schemes of all modulation schemes.

-

-

NR-5G Polar Encoder /Decoder

- The NR-5G Polar encoder/decoder is developed for 5G new radio.

- Fully compliant with 3GPP TS 38.212 Sections 5.2.1, 5.3.1, 5.4.1 and 5.5

-

LunaNet AFS LDPC Encoder and Decoder IP Core

- Rate 1/2

- GNSS, AFS

- Subframe 2/3/4

- Low implementation loss

-

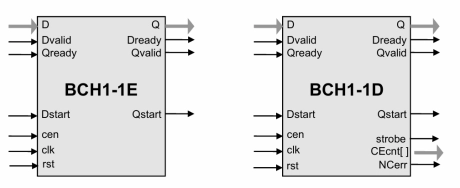

Very Low Latency BCH Codec

- High performance, low latency

- Small size (75K gates for k=298, t=4) configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

- Data inputs and outputs have flip-flops attached to the pins

-

Parameterizable compact BCH codec

- Highly parameterizable

- Very low area (in the largest, n = 511 t = 16 configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

-

BCH Intel® FPGA IP Core

- The Bose, Chaudhuri, and Hocquenghem (BCH) error correction intellectual property (IP) core is typically used in NAND flash applications

- The BCH Intel FPGA IP core is often used as a companion code with other forward error correction (FEC) IP cores, such as the Reed-Solomon and low-density parity-check (LDPC) IP cores.