Andes IP

Filter

Compare

47

IP

from

3

vendors

(1

-

10)

-

RVA23, Multi-cluster, Hypervisor and Android

- 64-bit out-of-order 4 wide decode 13-stage CPU core with 128 reordering buffers and 8 functional pipelines

- Symmetric multiprocessing up to 8 cores

- Private L2 cache support

- Level-3 shared cache and coherence support

-

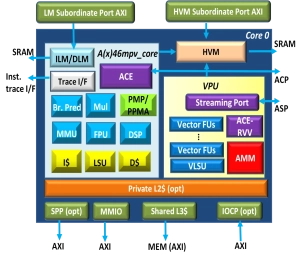

64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

- 2 different packages with or without vector: AX46MPV, AX46MP

- in-order dual-issue 8-stage CPU core with up to 2048-bit VLEN

- Symmetric multiprocessing up to 16 cores

- Private Level-2 cache

- Shared L3 cache and coherence support

-

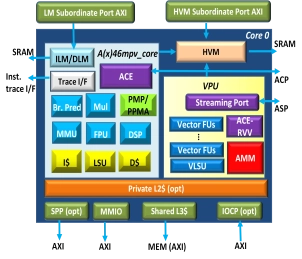

32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM

- AndesCore™ A46MP(V) 32-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture and Andes Matrix Multiply (AMM) extension.

- It supports RISC-V standard “G (IMA-FD)”, “ZC” compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector), CMO (cache management) extensions, Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

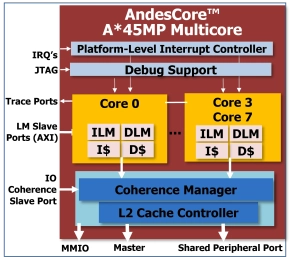

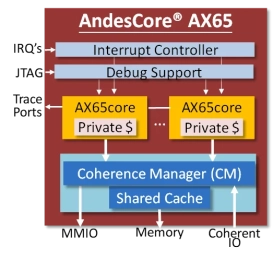

32-bit Multiprocessors with Level-2 Cache-Coherence

- The A45MP symmetric multiprocessor supports up to 4 cores and a level-2 cache controller with instruction and data prefetch.

- It manages level-2 cache coherence including I/O coherence for cacheless bus masters.

-

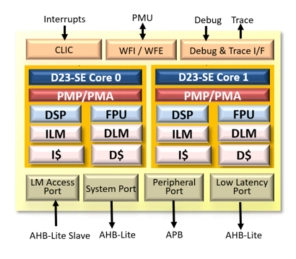

ISO26262 ASIL-B/D Compliant 32-bit RISC-V Core

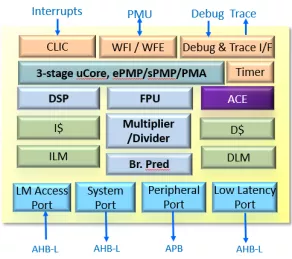

- The AndesCore™ D23-SE is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications with small gate count, and some dual-issue ability.

- In addition to commonly used RISC-V IMAC, single/double precision FPU and DSP extensions, it supports the recently ratified ISA extensions such as B (bit manipulation), K (scalar cryptography), CMO (cache management operations) as well as Zce (code size reduction), plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

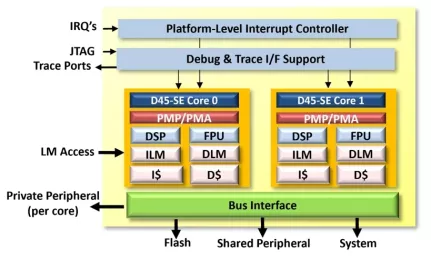

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications.

-

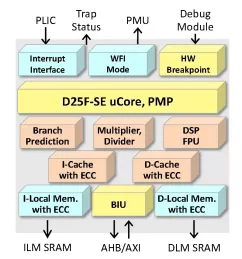

32-bit CPU IP core - ISO 26262 Automotive Functional Safety Compliant

- 32-bit CPU IP core that supports ISO 26262 ASIL B level functional safety for automotive applications

-

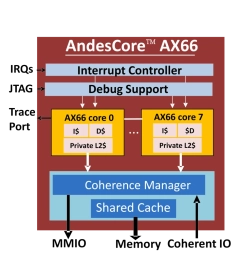

Superscalar Out-of-Order Execution Multicore Cluster

- 64-bit out-of-order 4 wide decode 13-stage CPU core with 128 reordering buffers and 8 functional pipelines

- Symmetric multiprocessing up to 8 cores

- Level-2 cache and coherence support

- AndeStar™ V5 Instruction Set Architecture (ISA)

- 64-bit architecture for memory space over 4GB

- TAGE Branch predication for highly accurate prediction

-

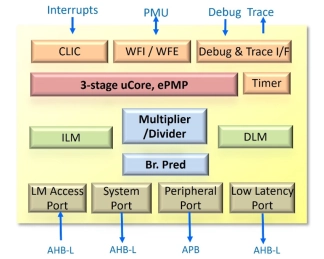

Compact and Performance Efficiency 32-bit RISC-V Core

- The N225 is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications with small gate count, and some dual-issue ability.

- In addition to commonly used RISC-V IMAC it supports the recently ratified ISA extensions such as B (bit manipulation) and Zce (code size reduction).

-

Compact, Secure and Performance Efficiency 32-bit RISC-V Core

- AndesCore™ D23 is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5/V5e architecture for embedded applications with small gate count, and some dual-issue ability.

- In addition to commonly used RISC-V I/EMAC, single/double precision FPU and DSP extensions, it supports the recently ratified ISA extensions such as B (bit manipulation), K (scalar cryptography), and CMO (cache management operations) as well as Zce draft (code size reduction).