28nm SerDes PHY IP

Filter

Compare

13

IP

from

6

vendors

(1

-

10)

-

SerDes PHY IP in TSMC (7nm, 12/16nm, 22nm, 28nm)

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

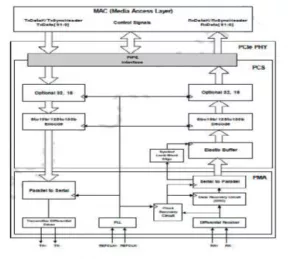

PCIe 4.0 Serdes PHY IP, Silicon Proven in TSMC 28HPCP

- Compliant with PCIe 4.0 Base Specification

- Compliant with PIPE 4.4

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s

- Supported physical lane width: x4

-

16Gbps multi-protocol programmable SerDes PHY in UMC 28HPC+

- Support PCIe G1 to G4 with PCS soft-macro supporting PIPE 4.4.1

- Support xPON applications: Sym/Asym GPON, Sym/Asym 10GPON, Sym EPON, Sym/Asym 10GEPON

-

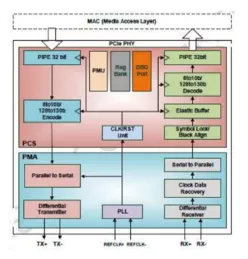

PCIe 4.0 Serdes PHY IP, Silicon Proven in UMC 28HPC

- Compliant with PCIe 4.0 Base Specification

- Compliant with PIPE 4.4

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s

- Supported physical lane width: x4

-

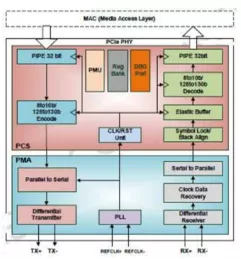

PCIe 3.0 Serdes PHY IP, Silicon Proven in UMC 28HPC

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

SERDES PHY IP

- Multi-protocol PHYs supporting data rate in the range of 1.25G to 10.3125Gbps

- Support >20dB channel loss

- Flexible ASIC interface for sharing impedance codes among multiple PMA hard macros and reducing the number of external reference resistors for impedance calibration.

- Support RX loss-of-signal detect

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 28HPCP

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

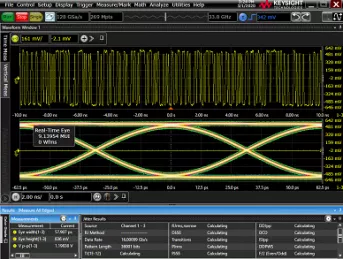

16G SerDes in 28nm

- ? Configurable data rate up to 16Gbps

- ? Multiple 8 lanes transceiver

- ? Internal high performance Frac-N PLL, support SSC

- ? 32bit parallel data bus

-

12.5G Multiprotocol Serdes IP, Silicon Proven in UMC 28HPC

- A universal SERDES IP that operation from 1Gbps to 12.5 Gbps

- Compatible with PCIe/USB3/SATA base Specification

- Support 40-bit/32-bit/20-bit/16-bit parallel interface

- Support for PCIe2(5.0Gbps), USB3.0(5.0Gbps) and SATA3(6.0Gbps)

-

12G Multiprotocol Serdes IP, Silicon Proven in SMIC 14SF+

- A universal SERDES IP that operation from 1Gbps to 12.5 Gbps

- Compatible with PCIe/USB3/SATA base Specification

- Support 40-bit/32-bit/20-bit/16-bit parallel interface

- Support for PCIe2(5.0Gbps), USB3.0(5.0Gbps) and SATA3(6.0Gbps)