General-Purpose I/O (GPIO) IP for TSMC

Welcome to the ultimate

General-Purpose I/O (GPIO) IP

for

TSMC

hub! Explore our vast directory of

General-Purpose I/O (GPIO) IP

for

TSMC

All offers in

General-Purpose I/O (GPIO) IP

for

TSMC

Filter

Compare

20

General-Purpose I/O (GPIO) IP

for

TSMC

from

4

vendors

(1

-

10)

Filter:

- 16nm

-

1.8V/3.3V I/O Library with 5V ODIO & Analog in TSMC 16nm

- A Flipchip I/O Library with dynamitcally switchable 1.8V/3.3V GPIO, 5V I2C/SM- Bus ODIO, 5V OTP Cell, 1.8V & 3.3V Analog Cells and associated ESD.

- A key attribute of this library is its ability to detect and dynamically adjust to a VDDIO supply of 1.8V or 3.3V during system operation.

-

1.8V/3.3V I/O library with ODIO and 5V HPD in TSMC 16nm

- A 1.8V/3.3V flip-chip I/O library with 4kV HBM ESD protection, I2C compliant ODIO and Hot-Plug Detect.

- This library is a production-quality, silicon-proven I/O library in TSMC 16nm technology.

- Supports multi-voltage GPIOs, capable of operating at 1.8V or 3.3V, dynamically selectable at the system level.

-

1.8V/3.3V GPIO Compliant with Multiple Standards in TSMC 16nm

- This library is a high-voltage GPIO I/O Macro in TSMC 16nm.

- The high-voltage GPIO is a flip-chip compatible 1.8V to 3.3V GPIO design, compliant with multiple I/O standards.

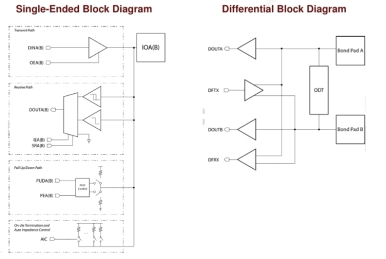

- It comes as a macro cell with a pair of I/Os in each cell, allowing differential I/O interface capabilities as well.

-

1.2V/1.8V GPIO Compliant with multiple standards in TSMC 16nm

- This library is a production-quality, silicon-proven I/O Library in TSMC 16nm technology.

- The High Performance GPIO is a flip-chip compatible, 1.2V to 1.8V GPIO design, compliant with multiple high-speed Single-Ended and Differential I/O standards.

- The macro cell comes as a pair of I/Os that can be configured as a differential I/O or two independent single- ended I/Os.

-

RGMII I/O offerings

- RGMII

- Physical Features

-

Secure Digital I/O offerings

- Secure Digital

- Physical Features

-

Open-drain I2C and SMBUS, DDC, CEC & HPD IO offerings

- I2C Open-drain

- Physical Features

-

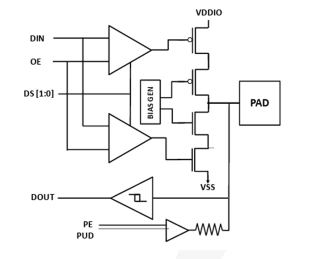

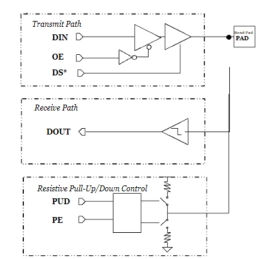

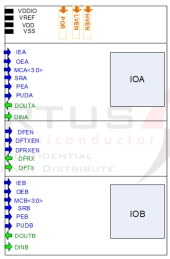

General IO at TSMC 16FFC Process

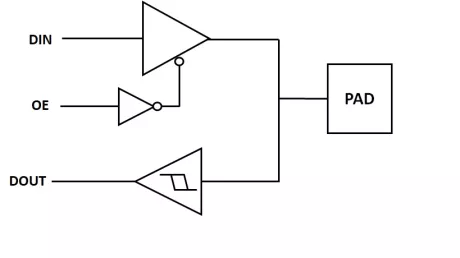

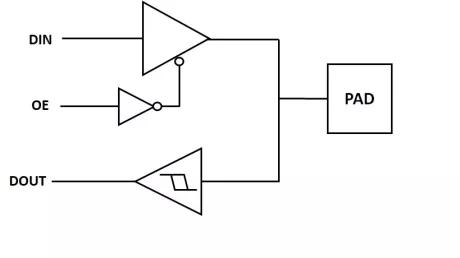

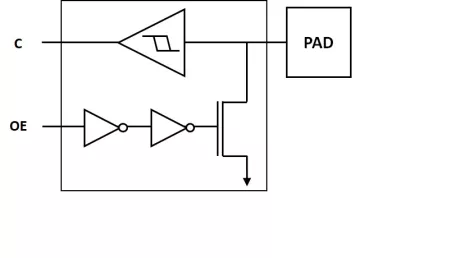

- Basic input/output unit for a chip with digital core

- Consisting of driver, receiver & pull-up/down resistors

- According to PAD arrangement, classified into two groups: Inline I/O & Stagger one.

- M31 also develops fail-safe or tolerance I/O for special application. The leakage current is inhibited when I/O power ramp down (Diagram A).

-

High-voltage solutions in baseline GlobalFoundries and multi-foundry technologies

- High-Voltage ESD

- Physical Features