General-Purpose I/O (GPIO) IP for TSMC

Welcome to the ultimate

General-Purpose I/O (GPIO) IP

for

TSMC

hub! Explore our vast directory of

General-Purpose I/O (GPIO) IP

for

TSMC

All offers in

General-Purpose I/O (GPIO) IP

for

TSMC

Filter

Compare

179

General-Purpose I/O (GPIO) IP

for

TSMC

from

8

vendors

(1

-

10)

-

1.2V Thin Oxide GPIO on TSMC 28nm RF HPC+

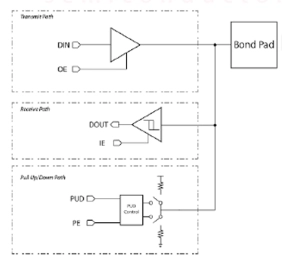

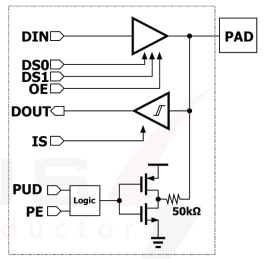

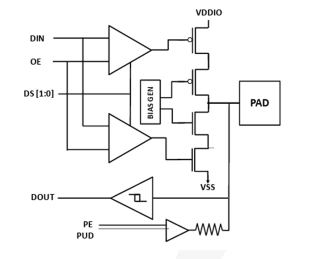

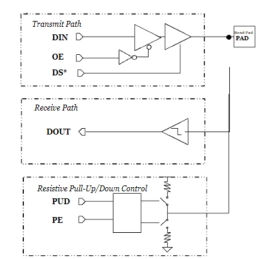

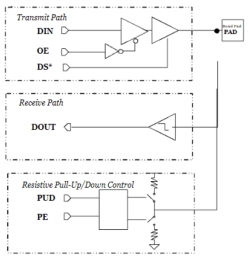

- The 1.2V Thin Gate GPIO is an IP macro for on-chip integration. It is a 1.2V general purpose I/O that does not rely on thick-gate devices. Only thin-gate, 0.9V capable core MOS devices are used in the design.

- Supported features include core isolation, programmable slew rate compensation, programmable drive strength, input/output enable, pull select and pull enable. Extra features such as programmable hysteresis can be supported upon request.

-

3.3V Capable GPIO on TSMC 28nm RF HPC+

- The 3.3V capable GPIO is an IP macro for on-chip integration. It is a 3.3V general purpose I/O built with a stack of 1.8V thick oxide MOS devices. It is controlled by 0.9V (core) signals.

- Supported features include core isolation, output enable and pull enable. Extra features such as input enable/disable, programmable drive strength and pull select, can be supported upon request.

-

1.8V Capable GPIO on Samsung Foundry 4nm FinFET

- The 1.8V capable GPIO is an IP macro for on-chip integration. It is a 1.8V general purpose I/O built with a stack of 1.2V MOS FINFET devices. It is controlled by 0.75V (core) signals.

- Supported features include core isolation, output enable and pull enable. Extra features such as input enable/disable, programmable drive strength and pull select, can be supported upon request.

-

Flipchip 1.8V/3.3V I/O Library with ESD-hardened GPIOs in TSMC 12nm FFC/FFC+

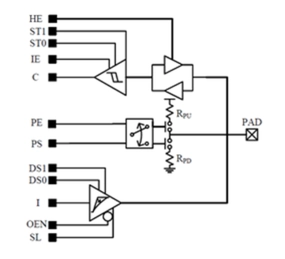

- A 1.8V/3.3V flip-chip I/O library with ESD-immune GPIOs and integrated POC circuitry in TSMC FFC/FFC+.

- This library is a production-ready I/O library built on the TSMC 12nm process. The library features 1.8V to 3.3V GPIOs with programmable drive strength, hysteresis, and control logic.

-

1.8V/3.3V I/O Library with 5V ODIO & Analog in TSMC 16nm

- A Flipchip I/O Library with dynamitcally switchable 1.8V/3.3V GPIO, 5V I2C/SM- Bus ODIO, 5V OTP Cell, 1.8V & 3.3V Analog Cells and associated ESD.

- A key attribute of this library is its ability to detect and dynamically adjust to a VDDIO supply of 1.8V or 3.3V during system operation.

-

1.8V/3.3V I/O library with ODIO and 5V HPD in TSMC 16nm

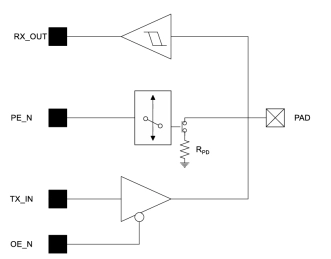

- A 1.8V/3.3V flip-chip I/O library with 4kV HBM ESD protection, I2C compliant ODIO and Hot-Plug Detect.

- This library is a production-quality, silicon-proven I/O library in TSMC 16nm technology.

- Supports multi-voltage GPIOs, capable of operating at 1.8V or 3.3V, dynamically selectable at the system level.

-

1.8V/3.3V I/O Library with ODIO and 5V HPD in TSMC 12nm

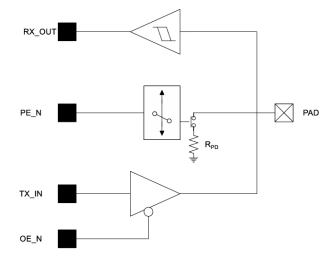

- A 1.8V/3.3V flip-chip I/O library with 4kV HBM ESD protection, I2C compliant ODIO and Hot-Plug Detect.

- This library is a production-quality, silicon-proven I/O library in TSMC 12nm technology.

- Supports multi-voltage GPIOs, capable of operating at 1.8V or 3.3V, dynamically selectable at the system level.

-

1.8V to 5V GPIO, 1.8V to 5V Analog in TSMC 180nm BCD

- A Flip-Chip compatible I/O Library in TSMC 180nm BCD with 1.8V to 5V GPIO, 1.8V to 5V analog, with ultra low-cap/low-leakage RF solutions.

- This silicon proven flip-chip compatible library in TSMC 180nm BCD features a multi-voltage GPIO, 1.8V to 5V analog I/O, and ultra-low capacitance and low leakage 36V+ ESD solutions. The library also includes 5V RF pads.

-

1.8V GPIO, 1.8V to 3.3V Analog in TSMC 180nm BCD

- A Flip-Chip compatible I/O Library in TSMC 180nm BCD with 1.8V GPIO, 1.8V to 3.3V Analog, with ultra low-cap/low-leakage 36V+ ESD solutions.

- This silicon proven flip-chip compatible library in TSMC 180nm BCD features a 1.8V GPIO, 1.8 to 3.3V analog I/O, and ultralow capacitance and low leakage 36V+ ESD solutions.

-

1.8V/3.3V GPIO Library with HDMI, Aanlog & LVDS Cells in TSMC 22nm

- A TSMC 22nm Inline, Flip Chip compatible library with GPIO, ODIO, HDMI, LVDS, & Analog Cells.

- This silicon-proven, flip chip compatible library in TSMC 22nm boasts a two speed GPIO: 75MHz and 150MHz.

- The library also features a 5V ODIO. GPIO and ODIO cells have an orientation of NS and EW.