LPDDR/mDDR IP for TSMC

Welcome to the ultimate

LPDDR/mDDR IP

for

TSMC

hub! Explore our vast directory of

LPDDR/mDDR IP

for

TSMC

All offers in

LPDDR/mDDR IP

for

TSMC

Filter

Compare

23

LPDDR/mDDR IP

for

TSMC

from

2

vendors

(1

-

10)

-

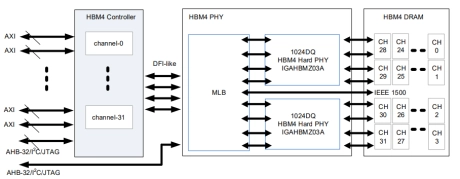

TSMC CLN3FFP HBM4 PHY

- IGAHBMZ03A is a High Bandwidth Memory 4 Physical Layer (HBM4 PHY) that is compliant with JEDEC HBM4 DRAM Specification JESD270-4.

- Fabricated in the TSMC 3 nm Advanced process node (N3P), it supports the data rate up to 12 Gbps per data pin in the DDR PHY Interface (DFI)-like 1:4 clock frequency ratio (HBM4 controller clock: WDQS = 1:4).

-

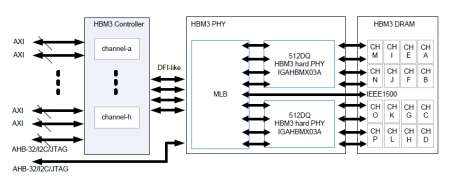

TSMC CLN7FF HBM3 PHY

- IGAHBMX03A is a HBM3 (High Bandwidth Memory) PHY IP compliant to the JEDEC HBM3 DRAM Specification Rev 0.95.

- Built on TSMC 7nm process node, it supports data rate up to 7200 Mbps per data pin with DFI 1:4 clock frequency ratio (controller clock : WCK = 1:4).

-

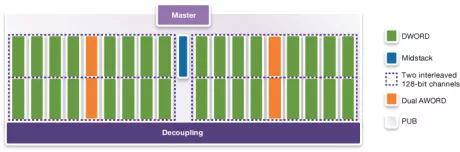

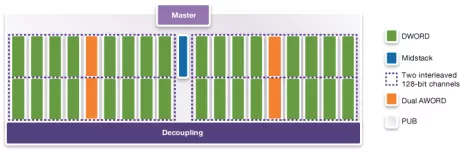

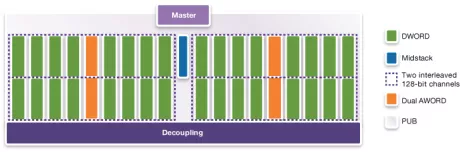

HBM3 PHY V2 (Hard) - TSMC N3P

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time

-

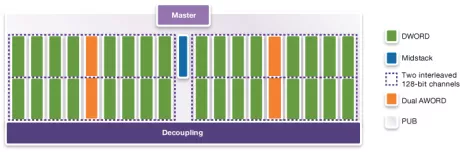

HBM2E PHY V2 - TSMC N5

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 - TSMC 7FF18

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 - TSMC 6FF18

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

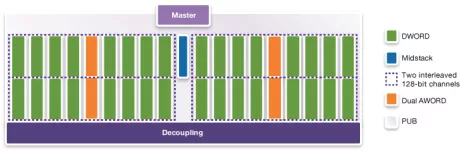

HBM2E PHY V2 (Hard 1) - TSMC 7FF18

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 (Hard 1) - TSMC 6FF18

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 (Hard 1) - TSMC 5FF12

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

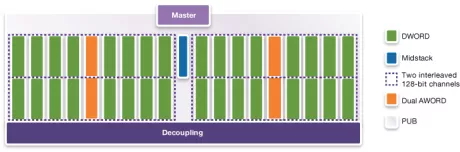

HBM3 PHY V2 - TSMC N5

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time