High-speed IP for GLOBALFOUNDRIES

Welcome to the ultimate

High-speed IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

High-speed IP

for

GLOBALFOUNDRIES

All offers in

High-speed IP

for

GLOBALFOUNDRIES

Filter

Compare

24

High-speed IP

for

GLOBALFOUNDRIES

from

10

vendors

(1

-

10)

-

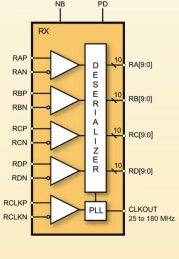

LVDS Deserializer IP

- The MXL-DS-LVDS is a high performance 4-channel LVDS Deserializer implemented using digital CMOS technology.

- Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 10 bits wide per channel. The input clock is 25MHz to 165MHz. The De-serializer is highly integrated and requires no external components.

-

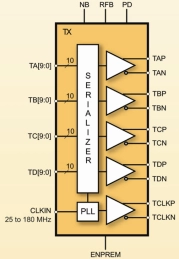

LVDS Serializer IP

- The MXL-SR-LVDS is a high performance 4-channel LVDS Serializer implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels.

- The parallel data width is programmable, and the input clock is 25MHz to 165MHz. The Serializer is highly integrated and requires no external components.

-

GF12 - 0.8V LVDS Rad-Hard Transceiver in GF 12nm

- The 2.5Gbps LVDS transceiver in GlobalFoundries LP/LP+ is designed for high-speed, low-power data transmission in radiation-intensive environments.

- Engineered with a Rad-Hard by Design approach, the Rad-Hard cells have been proton tested to 64 MeV with a flux exceeding 1.3E+09, and is latch-up proven to 200mA across -40C to 125C, ensuring robust immunity against TID, SEE, and SEL effects.

-

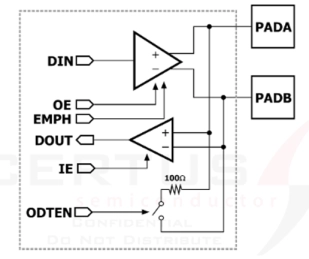

GF12 - 0.8V SLVS Rad-Hard Transceiver in GF 12nm

- This SLVS I/O Library delivers a robust, high-performance solution for high-speed differential signaling in GlobalFoundries 12nm process technology.

- Designed for optimal signal integrity, this 0.8V SLVS transceiver features fast rise and fall times, low propagation delay, and built-in pre-emphasis to enhance signal quality over longer traces.

- With support for data rates up to 3Gbps, it enables reliable, low-power communication while maintaining excellent noise immunity.

-

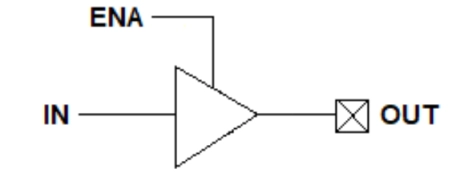

Automotive Grade 1 – Differential Output Driver on GLOBALFOUNDRIES 22FDX-AG1

- Differential output to chip core

- Wide frequency range support up to 2000MHz output for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Low power consumption

-

LVDS interfaces

- Wide operating range

- High data rates

- Very flexible programmability

- Excellent signal integrity

- TIA/EIA644A LVDS and sub-LVDS compatibility

- Receiver also compatible with LVPECL

-

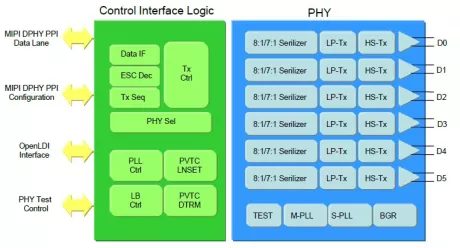

MIPI DPHY & LVDS Transmit Combo on GF55LPe

- MIPI D-PHY version 1.2 compliant PHY transmitter

- OpenLDI version 0.9 compliant LVDS transmitter

-

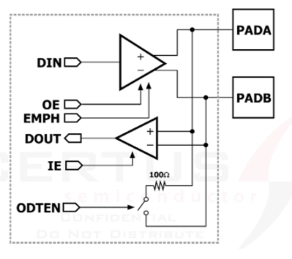

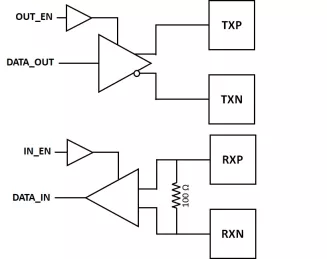

LVDS RX & TX IOs in multiple foundry technology

- LVDS TX

- LVDS RX

-

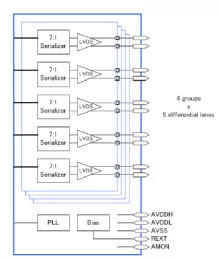

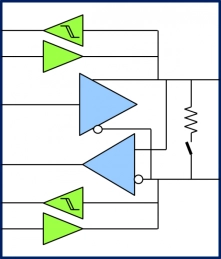

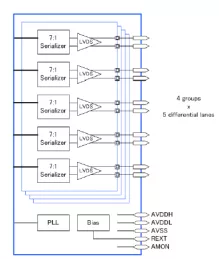

LVDS/FPD Link IP, Silicon Proven in GF 65/55LPe

- LVDS compliant Tx

- 4 groups of 4-Data

- 1-Clock channels Each lane/group can be turned on/off individually Data/Clock can be assigned to any lane within the group

- Differential polarity can be flip per lane

-

LVDS/FPD Link IP, Silicon Proven in GF 28LPe

- LVDS compliant Tx

- 4 groups of 4-Data

- 1-Clock channels Each lane/group can be turned on/off individually Data/Clock can be assigned to any lane within the group

- Differential polarity can be flip per lane