A/D Converter (ADC) IP for GLOBALFOUNDRIES

Welcome to the ultimate

A/D Converter (ADC) IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

A/D Converter (ADC) IP

for

GLOBALFOUNDRIES

All offers in

A/D Converter (ADC) IP

for

GLOBALFOUNDRIES

Filter

Compare

46

A/D Converter (ADC) IP

for

GLOBALFOUNDRIES

from

16

vendors

(1

-

10)

-

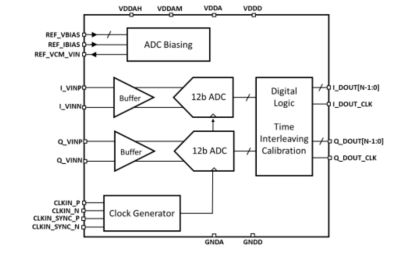

12-bit, 4 GSPS High Performance IQ ADC in GF22FDX

- GF22FDX Process

- 12-bit resolution, 4GSPS update rate

- Dual ADC configured as IQ Pair

-

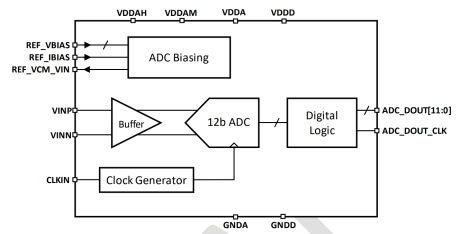

12 bit, 500 MSPS ADC on GF 22FDX

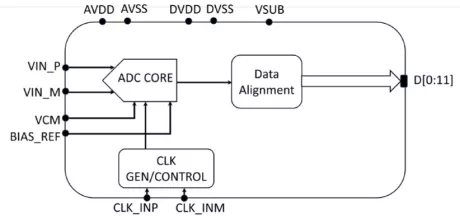

- The ODT-ADS-12B500M-G22FDX is an ultra-low power ADC designed in a 22nm CMOS process.

- This 12-bit, 500MSPS ADC supports input signals up to 100MHz and features a differential full-scale range of 0.8Vpp and excellent static and dynamic performance.

- The ADC architecture is optimized to maximize performance while minimizing power and area consumption. The ADC includes an integrated input buffer.

-

12-bit, 2 GSPS High Performance ADC in 12nm CMOS

- The ODT-ADS-12B2G-12nm is an ultra-highperformance time-interleaved ADC designed in a 12nm CMOS process.

- This 12-bit, 2GSPS ADC supports input signals up to 1.0 GHz and features a differential full-scale range of 0.8Vpp and excellent static and dynamic performance.

-

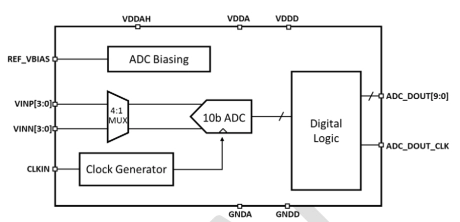

10-bit, 5 MSPS ADC in 12nm CMOS on GF 12nm LP+

- The ADC is an ultra-low-power ADC designed in a GF 12nm LP+ process.

- This 10-bit, 5MSPS ADC supports input signals up to 1 MHz and features 2V differential full-scale input range with excellent static and dynamic performance. The input front-end includes a 4:1 mux.

-

11-bit, 5 GSPS SAR ADC - GlobalFoundries GF22FDX

- The A11B5G is a low-power, high-speed analog to digital converter (ADC) intellectual property (IP) design block.

- It is a hybrid-SAR ADC, with 11-bit resolution and a sampling rate of 5 gigasamples-per-second (GSPS).

-

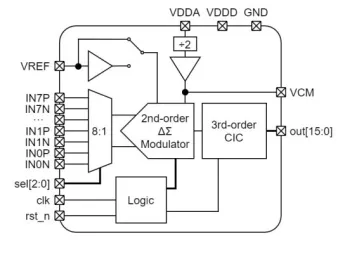

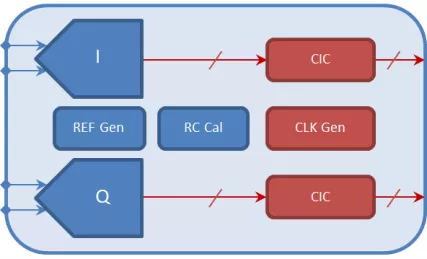

12-bit 40nm 1.1V 64MHz-to-340MHz continuous-time Delta-Sigma ADC

- Integrated Dual-Channel Continuous-time Delta-Sigma Modulator (I + Q)

- Integrated Dual decimate-by-8 Cascaded-Integrator-Comb Decimation Filter

-

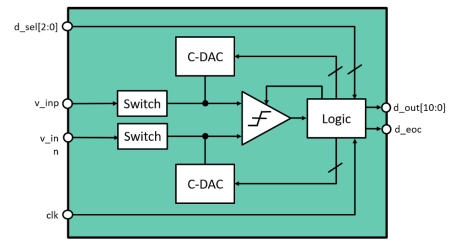

11 Bit 100 kS/s Ultra-Low Power SAR ADC on GlobalFoundries 22FDSOI

- The ADC IP is a general-purpose successive approximation converter for low-power medium resolution applications. Sample rate, resolution and power consumption are configurable.

- It is built using typical differential capacitor-DAC architecture, clocked comparator and bootstrapped switches. No additional reference voltage is required, achieving lmost rail-to-rail input. The target applications are environmental and biomedical signal processing.

-

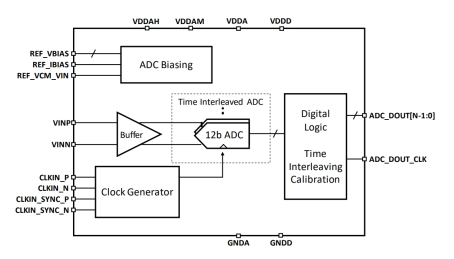

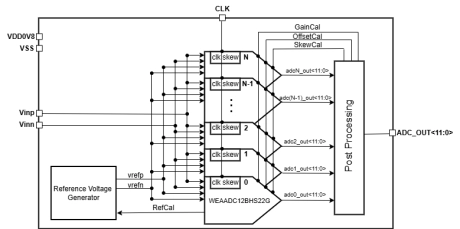

12-bit 2GSPS Time Interleaved ADC

- The WEAADC12BHSI22G is a 12-bit time interleaved Successive Approximation Analog-toDigital Converter (ADC) that supports both singleended and differential operation, depending on the input and reference connections

- It integrates 13 WEAADC12BHS22G with programmable clock skew (50ps coarse 4ps fine with minimum step 0.25ps) and pre/post-calibration logic on each

- Operating on a 0.8 V power supply, the WEAADC12BHSI22G can provide output up to 2GSPS in 13-interleaved mode

- The ADC can be clocked with 2GHz clock

-

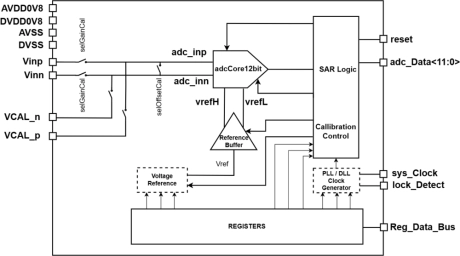

12-bit High Speed Analog to Digital Converter

- The WEAADC12BHS22G is a 12-bit Successive Approximation Analog-to-Digital Converter (ADC) that supports both single-ended and differential operation, depending on the input and reference connections

- It integrates a split-capacitor DAC with a built-in track-and-hold circuit, a dynamic comparator with DC-offset autocalibration, SAR logic state machine, and pre/post-calibration logic

- The device also includes gain and offset calibration mechanisms

- Operating on a 0.8 V power supply, the WEAADC12BHS22G requires 13 clock cycles for conversion, in 12-bit resolution mode, with digital data available at the rising edge of the 14th clock pulse

-