USB is the ubiquitous peripherals interconnect of choice for large number of computing and consumer applications. Many systems provide a comprehensive set of drivers to support all commonly available USB peripherals. This enables consumer to purchase and use USB peripherals without having to install a new driver, thus strengthening the popularity of USB. In addition, Arasan supplies USB silicon, so costs are normally very low for product manufacturing of USB hosts and peripherals.

It is becoming increasingly attractive to use USB as a chip-to-chip interconnect within a product (without use of external cables and connectors). However, because USB was designed to enable hot-plugging of peripherals over cables up to 5 meters in length, there are certain power and implementation issues that are not attractive for many chip-to-chip interconnect solutions.

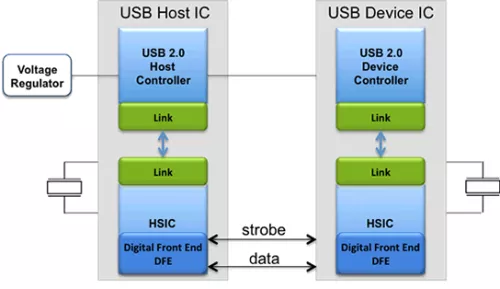

To better meet the needs of a USB chip-to-chip interconnect, HSIC accomplishes this by removing the analog transceivers, thus reducing complexity, cot and manufacturing risk.

HSIC is a 2-signal (strobe, data) source synchronous serial interface which uses 240Mhz DDR signaling to provide High-Speed 480Mps USB transfers which are 100% host driver compatible with traditional USB cable-connected topologies. Full-Speed (FS) and Low-Speed (LS) USB transfers are not directly supported by the HSIC interface (a HSIC enables hub can provide FS and LS support, as well as IC_USB support).

USB HSIC PHY - High Speed Inter-Chip IP Core

Overview

Key Features

- High-Speed 480Mbps data rate only

- Source-synchronous seriel interface

- No power consumed unless a transfer is in progress.

- Maximum trace length of 10cm

- No hot Plug-n-Play support, no hot removal/attach

- Signals driven at 1.2V standard LVCMOS levels

- Designed for low-power applications

- No high-speed chirp protocol, the HSIC interface is always operated at high-speed

- HSIC host or peripheral can be powered in any order

Benefits

- Silicon proven

- Performance and Power efficient interface

- Leverages USB infrastructure

Block Diagram

Deliverables

- GDS-II

- CDL netlist for LVS

- DRC and Antenna reports

- LIB files

- Userguide and Integration Guides

- LEF

- Scan-inserted netlist for DFT

- Verification Environment with behavioral models

Technical Specifications

Short description

USB HSIC PHY - High Speed Inter-Chip IP Core

Vendor

Vendor Name

Maturity

Silicon Proven

Availability

Now

Related IPs

- High Speed Inter-CHIP USB 2.0 PHY

- USB 2.0 PHY IP core

- USB 1.1 PHY, Support Low Speed and Full Speed - HHGrace 110nm

- USB 1.1 PHY, Support Low Speed and Full Speed - HLMC 55nm

- High Channel Count DMA IP Core for PCI-Express

- USB 2.0 Hi-Speed OTG Controller Subsystem w/AHB Interface Supporting HSIC (config. as Device only or Full Speed only)