GammaCORE UCIe D2D Controller IP enables multi-die applications, such as the connection of I/O chiplets to a main die, accelerator die to a processor die, multi-die packet processors, multi-die Ethernet switches, etc.

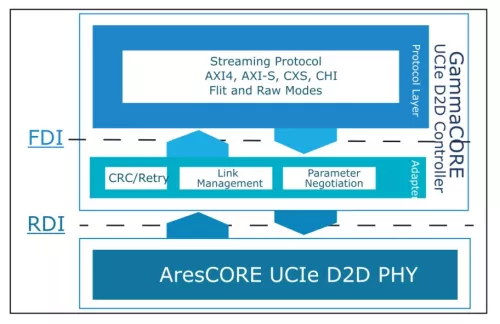

GammaCORE Controller IP core consists of the Streaming Protocol Layer, to extend the SoC interface across the UCIe link, and the Adapter Layer, to provide a reliable end-to-end link.

On the UCIe link side, GammaCORE provides seamless connection to the AresCORE UCIe D2D PHY IP through the RDI interface. On the system side, GammaCORE connects to one or multiple internal SoC interfaces.