AMBA APB Synthesizable Transactor provides a smart way to verify the AMBA APB component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's AMBA APB Synthesizable Transactor is fully compliant with standard AMBA APB 3.0/4.0 Specification and provides the following features

AMBA APB Synthesizable Transactor

Overview

Key Features

- Compliant to ARM AMBA APB 3.0/4.0 protocol

- Supports AMBA APB Master, APB Slave

- Supports multiple slaves

- Supports all ARM AMBA APB 3.0/4.0 data and address widths

- APB3/APB4 common support

- Different transfer types including IDLE, WRITE and READ

- Unaligned address accesses

- Slave memory map support

- Unmapped address accesses

- Flexibility to send completely configured data

- Slave supports fine grain control of response per address or per transfer

- Programmable wait state insertion

- Programmable timeout insertion

- Programmable number of idle cycles

- Ability to inject errors during data transfer

- APB4 support

- In addition to APB3 support, APB4 supports the following features:

- Protected accesses

- Write strobe signal to enable sparse data transfer on the write data bus

- Supports FIFO memory

- Supports on-the-fly protocol and data checking

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

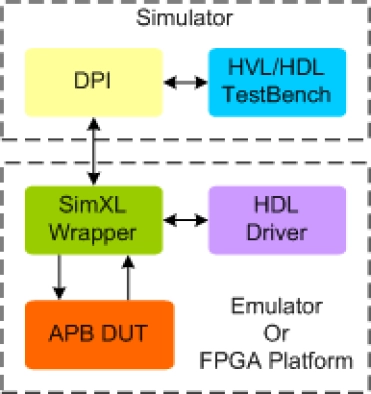

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the APB testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Technical Specifications

Short description

AMBA APB Synthesizable Transactor

Vendor

Vendor Name

Related IPs

- AMBA LPI Synthesizable Transactor

- SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus

- SPI Controller IP- Master-only, Parameterized FIFO, AMBA APB / AHB / AXI Bus

- 100% Secure Cryptographic System for RSA, Diffie-Hellman and ECC with AMBA AHB, AXI4 and APB

- Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- Ethernet 100G Synthesizable Transactor