AMBA LPI Synthesizable Transactor provides a smart way to verify the AMBA LPI component of a SOC or an ASIC in Emulator or FPGA platform. The SmartDV's AMBA LPI Synthesizable Transactor is fully compliant with standard AMBA LPI Specification and provides the following features.

AMBA LPI Synthesizable Transactor

Overview

Key Features

- Compliant to ARM AMBA LPI protocol.

- Support LPI Master and LPI Slave.

- LPI support

- Supports LPI Q-Channel interface, P-Channel interface operations.

- Programmable Timeout insertion.

- Rich set of configuration parameters to control AMBA LPI functionality.

- On-the-fly protocol checking.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Callbacks in master and slave for various events.

- Status counters for various events on bus.

Benefits

- Compatible with testbench writing using SmartDV VIP's

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

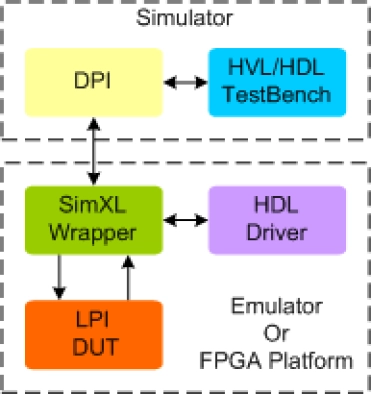

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the AMBA LPI Synthesizable testcases.

- Examples showing how to connect various components, and usage of Synthesizable Transactor.

- Detailed documentation of all class, task and functions used in verification env.

- Documentation also contains User's Guide and Release notes.

Technical Specifications

Short description

AMBA LPI Synthesizable Transactor

Vendor

Vendor Name