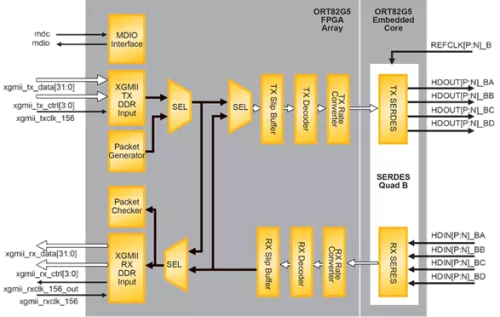

The 10 Gigabit Ethernet Extended Sublayer (XGXS) Intellectual Property (IP) Core enables the creation of system solutions for 10 Gigabit Ethernet (10 GbE) applications as defined by IEEE 802.3ae. This IP Core targets the pro-grammable array section of the ORCA ORT82G5 FPSC and provides a bridging function between 10 Gigabit Media Independent Interface (XGMII) and 10 Gigabit Attachment Unit Interface (XAUI) devices.

The ORT82G5 is a high-speed transceiver with an aggregate bandwidth of up to 29.6 Gbits/s that is targeted towards users in need of high-speed backplane and chip-to-chip interfaces using Ethernet and Fibre-Channel based protocols. The ORT82G5 has eight channels of integrated 0.6-3.7 Gbits/s SERDES channels that can be used as 2x10 Gbits/s XAUI interfaces.

XAUI is a high-speed interconnect that offers reduced pin count and is specified to drive up to 20 inches of PCB trace on standard FR-4 material. Each XAUI interface comprises four self-timed 8b/10b encoded serial lanes each operating at 3.125 Gbits/s and thus is capable of transferring data at an aggregate rate of 10 Gbits/s.

XGMII is a 156MHz Double Data Rate (DDR), parallel, short-reach interconnect interface (typically less than two inches). It supports interfacing to 10Gb/s Ethernet Media Access Control (MAC) and PHY devices.

In this design, the XGXS core is implemented in the FPGA portion of the device. A packet generator/checker and MDIO interface are also implemented in the FPGA logic.

The XGXS IP core is provided with implementation scripts, test benches, and documentation to allow users to integrate the functions for 10 GbE LAN/WAN applications.

10Gb Ethernet XGXS

Overview

Key Features

- Complete 10Gb Ethernet Extended Sublayer (XGXS) Solution Based on the ORCA ORT82G5 0.6-3.7 Gbit/s 8b/10b Backplane Interface FPSC.

- IP Targeted to the ORT82G5 Programmable Array Section Implements Functionality Conforming to IEEE Standard 802.3ae, Including:

- 10 GbE Media Independent Interface (XGMII).

- Slip buffers for clock domain transfer to/from the XGMII interface.

- Complete translation between XGMII and XAUI PCS layers, including 8b/10b encoding and decoding of Idle, Start, Terminate, Error and Sequence code groups and sequences, and randomized Idle generation in the XAUI transmit direction.

- 64-bit data/8-bit control packet generator/checker on the XGMII side that supports standard compliant CRPAT and CJPAT generation and checking for XAUI interoperability testing.

- Standard compliant MDIO/MDC interface.

- Automatic initialization and synchronization of the embedded core.

- Interface with the high-speed SERDES block embedded in the ORT82G5 that implements a standard XAUI.

- XAUI Functionality Supported by the Embedded Portion of the ORT82G5, Including:

- Eight channels of 3.125 Gbits/s serializer/deserializer with 8b10b encoding/decoding (four SERDES channels are used in this application).

- XAUI compliant lane-by-lane synchronization.

- Lane deskew functionality.

Block Diagram

Technical Specifications

Related IPs

- 10-Gbit Ethernet MAC

- Ethernet Controller - Configurable MAC solutions for speeds from 10Gbps to 10Mbps

- Ethernet SerDes - 16Gbps and 10Gbps multi-protocol SerDes PHY

- Ethernet 10GBase-KR Synthesizable Transactor

- 10GBase-KR Ethernet Verification IP

- 10G/2.5G/1G Multi-Speed Ethernet Controller IP for Automotive Applications