Inline Memory Encryption IP

Welcome to the ultimate Inline Memory Encryption IP hub! Explore our vast directory of Inline Memory Encryption IP

All offers in

Inline Memory Encryption IP

Filter

Compare

9

Inline Memory Encryption IP

from 2 vendors

(1

-

9)

-

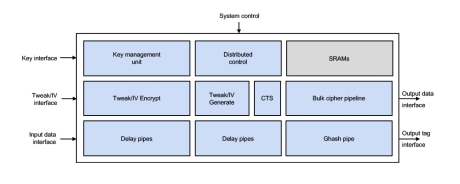

Fast Inline Cipher Engine, AES-XTS/GCM, SM4-XTS/GCM, DPA

- One input word per clock without any backpressure

- Design can switch stream, algorithm, mode, key and/or direction every clock cycle

- GCM: throughput is solely determined by the data width, data alignment and clock frequency

- XTS: block processing rate may be limited by the number of configured tweak encryption & CTS cores; a configuration allowing 1 block/clock is available

-

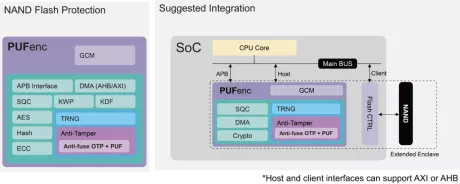

External NAND flash protection, designed to secure stored assets with a local key from PUF

- PUFenc is designed to protect external flash memory and its stored assets.

- The IP provides asset encryption, such as a learning model for AI or firmware for the chip with a local key from the PUF.

- It adds an additional layer of security by avoiding using the global key, which is a shared key among ICs after the chip leaves the manufacturing floor.

-

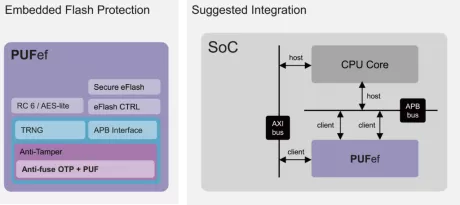

Embedded Flash Protection with Hardware Root of Trust and Lite Crypto Engine

- PUFef is designed to protect embedded Flash with a Hardware Root of Trust and a lite crypto engine of RC6.

- The RC6 provides a comprehensive level of security while also minimizing overall size.

- Before attempting to hack the crypto engine, attackers would first have to destroy the embedded Flash.

-

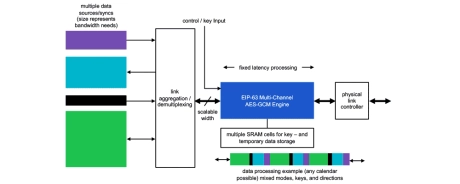

Inline cipher engine for PCIe, CXL, NVMe, 5G FlexE link integrity and data encryption (IDE) using AES GCM mode

- The ICE-IP-63 (EIP-63) is a scalable high-performance, multi-channel cryptographic engine that offers AES-GCM operations as well as AES-CTR and GMAC on bulk data.

- Its flexible data path is suitable to scale from 100 Gbps to 2.4 Tbps to provide a tailored engine with minimal area for your application.

- The FIFO-like data interface makes it possible to perform frame processing for many different protocols, including MACsec, IPsec, and OTN security.

-

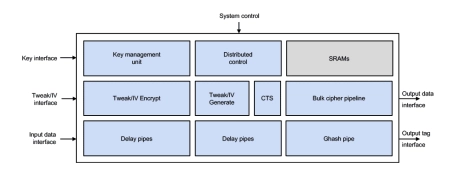

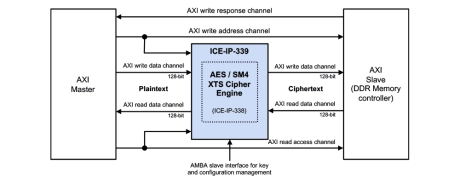

High-speed Inline Cipher Engine

- The ICE-IP-338 data path can be scaled to widths that are multiples of 128 bit to allow a tradeoff between area and performance that best fits the target application.

- Configuration options include or exclude support for CipherText Stealing (CTS), the GCM mode, and the SM4 algorithm and/or Datapath Integrity logic.

- The cryptographic AES and SM4 primitives can be provided with or without side channel attack DPA countermeasures.

-

Inline cipher engine with AXI, for memory encryption

- Throughput: 128 bit (16 Byte) wide encryption/decryption per cycle

- Throughput: 1 tweak computation per 4 clock cycles

- Bidirectional design including arbitration between read and write requests

- Zero clock overhead for switching between encryption (write) and decryption (read)

- 30-40 cycle data channel latency

-

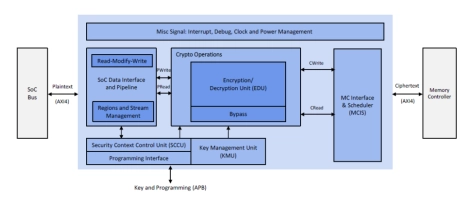

Inline memory encryption engine, for FPGA

- Performs encryption, decryption and/or authentication using AES Counter Mode (CTR) or Galois Counter Mode (GCM)

- Supports AES key sizes 128 or 256

- Internal key management with NIST-compliant key generation

- Encrypt memory space into user-defined vaults, each with a unique key

- Compatible with AMBA AXI4 interface

- Supports hard or soft memory controllers in Xilinx FPGA and SoC devices

- Supports multiprocessor systems

-

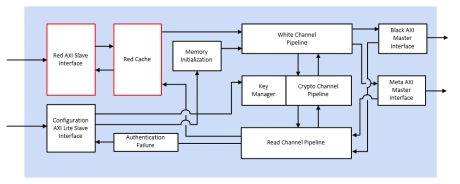

Inline memory encryption engine for ASIC SoCs

- 128/512-bit (16-byte) encryption and decryption per clock cycle throughput

- Bidirectional design including separate crypto channels for read and write requests, ensuring non-blocking Read

- Read-modify-write supporting narrow burst access.

- Zeroization and support for memory initialization

- Latency: <28 clock cycles for unloaded READ

-

In-line Multi-Protocol Cipher Engine

- IPSec (IPv4 and IPv6):

- and 6379),

- MACsec

- 802.1AE