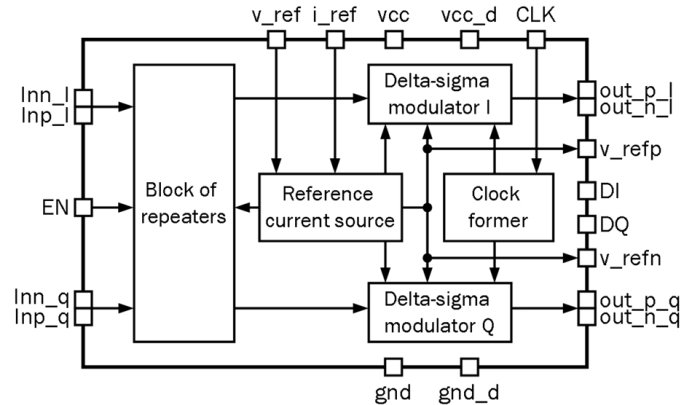

The cell is a second order delta-sigma dual channel (I/Q) analog-to-digital converter that supports sample rates up to 8.5 kHz and oversampling ratio 128. This structure is based on the principle of commutated capacitors and consists of two differential channels. Input signal bandwidth 0...8.5 kHz.

The block is fabricated on iHP SiGe BiCMOS 0.25 um (SGB25V) technology.

1-bit 2-channel 2.2 MSPS (8.5 kHz BW) delta-sigma ADC

Overview

Key Features

- iHP SGB25V

- Small area

- Low current consumption

- Operating frequency range of 0 …8.5 kHz

- Oversampling ratio 128

- No external components required

- Portable to other technologies (upon request)

Block Diagram

Applications

- Receivers, transmitters, transceivers

- Analog integrated circuits

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

1-bit 2-channel 2.2 MSPS (8.5 kHz BW) delta-sigma ADC

Vendor

Vendor Name

Foundry, Node

iHP SiGe BiCMOS 0.25 um

Maturity

Silicon proven

Availability

Now

Related IPs

- 9-bit 2-channel 0.5 to 33 MSPS (8 to 500 kHz BW) delta-sigma ADC

- 16-bit 2-channel 25 kHz bandwidth delta-sigma stereo, audio DAC

- 12-bit 2-channel 5 to 7.5 MSPS cascade delta-sigma ADC

- 12 bit, 500 MSPS ADC on GF 22FDX

- 12-bit 40nm 1.1V 64MHz-to-340MHz continuous-time Delta-Sigma ADC

- 12-bit 2-channel up to 50 MSPS current steering DAC