Optimizing Communication and Data Sharing in Multi-Core SoC Designs

作者:Andy Nightingale, Arteris 产品管理和营销副总裁

随着半导体制造技术的进步,片上系统(SoC)提高了我们在更小面积内容纳更多晶体管的能力,从而实现更高的计算能力和功能。为了支持不断增长的数据通信需求,SoC 中连接组件的方式需要不断发展。

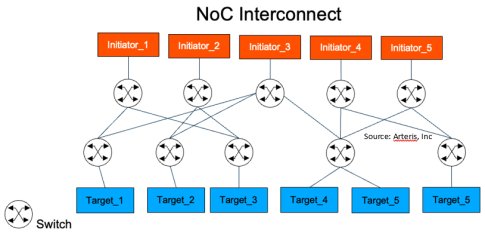

片上网络(NoC)互连用于有效管理组件之间的数据流,提供可扩展的低延迟和高能效通信,从而实现 CPU、GPU、NPU 和其他加速器等功能的无缝集成。NoC 可减少数据瓶颈,提高系统性能,并适应 SoC 设计中日益增加的复杂性。

解码缓存一致性

缓存一致性是 SoC 中各组件之间高效数据共享的核心。它是一种保证数据一致性的机制,可防止瓶颈和数据不一致,并最终维持整体系统性能。它确保系统在后台无缝运行。

深入研究缓存一致性的工程师会发现自己处于硬件和软件的交叉点。在这一领域,确保数据在多核系统中保持一致的错综复杂的技术问题占据了首位。缓存一致性是贯穿现代技术复杂结构的基本主线,可确保所有进程的内存视图一致。

互连技术的发展

随着半导体技术的进步,元件通信的方法也在不断发展。以下是对不同互连结构的技术探索:

(Source: Arteris, Inc.)

20 世纪 90 年代,流行的总线结构是共享总线。当一个组件需要与另一个组件通信时,它会将数据放到总线上,允许所有连接的组件读取数据并在必要时做出响应。虽然共享总线的概念简单明了,但它引入了总线争用和带宽有限等复杂问题,尤其是当更多组件集成到系统中时。

本世纪初,分层总线作为一种解决方案出现,用于管理和简化分层功能中组件之间的数据流。它们提供了高效的数据流、可扩展性、模块化设计,并降低了复杂性。然而,它们也带来了潜在的挑战,包括延迟、有限的带宽、布线复杂和功耗增加。

2005 年前后,各种交叉(crossbar)总线应运而生。它们提供了高速同步连接,减少争用,并最大限度提高了带宽。根据设计和技术的不同,crossbar 实施的复杂性、成本和可扩展性也各不相同。一些crossbar 实现方式复杂且成本高昂,而另一些则对于大型系统更具可扩展性。

片上网络(NoC)的概念也开始在研发领域流行起来。与许多新技术概念一样,基于 NoC 的互连在商业半导体设计中得到广泛采用又花了几年时间。

Crossbar总线与 NoC 总线

Crossbar总线有几个优点和缺点。当高速同步连接数量有限的元件时,它们具有很高的效率,是高性能 CPU 和内存访问等应用的理想选择。但是,它们在实施时可能具有挑战性,并且在处理大型异构 SoC 设计时可能无法很好地扩展。

(Source: Arteris, Inc.)

另一方面,NoC 架构因其可扩展性和适应性,在现代 SoC 设计中越来越受欢迎。它们非常适合具有众多异构组件(包括多核处理器、图形处理器、加速器和外设)的复杂 SoC。NoC 可有效管理这些系统中的通信,并实现灵活的资源分配。它们在 SoC 设计中解决各种应用的可扩展性挑战方面尤为重要。

互连技术的选择最终取决于 SoC 的具体设计目标、功耗性能和可扩展性要求。

(Source: Arteris, Inc.)

缓存一致性互连与非一致性互连

一致性互连可确保系统内的所有进程具有统一一致的内存视图。相比之下,非一致性互连不能保证这种一致性,可能需要直接明确的数据管理。选择一致性互连还是非一致性互连取决于特定系统的需求和设计考虑。

为了说明这种区别,请考虑一个带有机器学习子系统的系统。在这样的设置中,机器学习处理器独立管理数据流,强加缓存一致性可能会带来不必要的开销。

(Source: Arteris, Inc.)

另一方面,多核 SoC 设计是一致性 NoC的典型例子,例如 iPhone 和 iPad 中的Apple A17 Bionic 或 Android 智能手机中的高通 Snapdragon 888。在这些设备中,保持缓存一致性可确保正确的程序执行和数据一致性。

数据访问和效率

缓存作为高速存储层,可临时存储频繁访问的数据和指令,与内存或硬盘等较慢的存储介质相比,可显著提高数据访问速度。从智能手机和笔记本电脑到服务器和超级计算机,各种设备中都有这些不可或缺的缓存组件。缓存通常分为多个级别,包括 L1、L2 和 L3 缓存,每个级别比前一个级别的缓存容量更大,但访问时间比前一个级别稍慢。其主要目的是通过将常用数据保存在靠近 CPU 的位置,最大限度地减少 CPU 等待数据的时间。这样可以提高整体性能、减少延迟并提高能效。此外,它们还能有效管理内存带宽,具有成本效益。

管理缓存会增加复杂性,需要进行一致性管理。虽然缓存一致性可以防止数据不一致并确保正确性,但它也存在一些挑战。例如,同步缓存更新会无意中引入数据不一致,增加延迟和资源消耗。可扩展的缓存需要高效的协议和同步软件来确保数据一致性,避免数据擦除和差异等问题,从而使一致性变得更加困难。

应对这些挑战的技术要求为工程师带来了机遇。他们必须深入研究缓存一致性协议的设计。每种协议都有自身的一系列技术挑战和权衡。工程师必须评估其系统的具体需求,并选择最符合其性能和效率目标的协议。这一技术决策过程可以决定项目的成败。

Arteris的Ncore缓存一致性互连解决方案

为了追求卓越的技术,Arteris 推出了 Ncore,这是一种灵活、可扩展的互连解决方案,旨在应对缓存一致性和数据流的复杂性。它提供异构一致性,在复杂的 SoC 设计中提供灵活性、性能优化、能效和易开发性。它可确保各种处理元件之间的数据一致性,从而提高系统的效率和性能。此外,它还利用可配置的代理缓存,动态适应不同的系统配置。这些缓存可根据特定的一致性要求进行定制,从而实现高效的数据共享,并最大限度地减少一致性流量。Ncore 的多种可配置监视过滤器能实现更有针对性和更简化的一致性管理,从而降低了设计的整体复杂性。这种方法确保了高效和量身定制的一致性解决方案,有助于提高整体效率。

(Source: Arteris, Inc.)

总结

半导体技术的飞速发展要求优化多核 SoC 设计中的通信和数据共享。从共享总线到分层总线和crossbar总线的发展,催生了 NoC 架构,尤其是在解决复杂多样的 SoC 配置所带来的复杂性方面。缓存一致性作为基本要素,可确保数据一致性和系统性能,而在一致性互连和非一致性互连之间做出选择则取决于具体的设计考虑因素。

缓存在提高数据访问速度方面的作用至关重要,但它也给一致性管理带来复杂性。工程师在选择缓存一致性协议时面临着关键决策,需要克服技术挑战,权衡利弊,以实现性能和效率目标。随着 SoC 技术的发展,优化通信、有效管理缓存一致性,以及就互连技术做出明智决策,变得越来越重要。提供灵活、可扩展的互连选项的解决方案,标志着在应对这些不断变化的挑战方面取得了重大进展。

了解更多关于 Arteris的 缓存一致性 和 非一致性 IP 。

Andy Nightingale 是 Arteris 产品管理和营销副总裁,他在高科技行业拥有超过 35 年的经验,其中包括在 Arm 担任各种工程和产品管理职位 23 年。

Related Semiconductor IP

- Verification IP for NVMe

- Verification IP for CXL

- 128-Point FFT/IFFT IP Core

- APB Post-Quantum Cryptography Accelerator IP Core

- Very fast VMAF accelerator