Arm與台積公司展示業界首款7奈米Arm核心 CoWoS®小晶片系統以支援高效能運算應用

發佈日期 : 2019/09/26

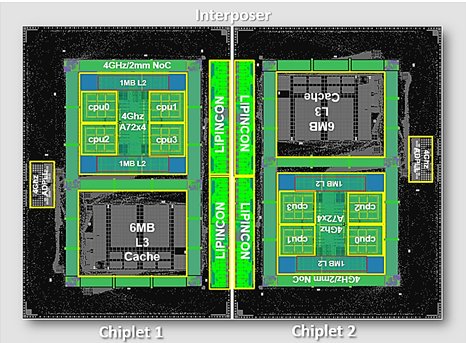

高效能運算領域的領導廠商Arm與台積公司今(26)日共同發表業界首款採用台積公司先進的CoWoS®封裝解決方案並獲得矽晶驗證的7奈米小晶片(Chiplet)系統,其中內建Arm®多核心處理器。此款概念性驗證的小晶片系統成功地展現在7奈米FinFET製程及4GHz Arm核心的支援下打造高效能運算的系統單晶片(System-on-Chip, SoC)之關鍵技術。同時也向系統單晶片設計人員演示運作時脈4GHz的晶片內建雙向跨核心網狀互連功能,及在台積公司CoWoS中介層上的小晶片透過8Gb/s速度相互連結的設計方法。

不同於整合系統的每一個元件放在單一裸晶上的傳統系統單晶片,將大尺寸的多核心設計分散到較小的小晶片設計更能完善支持現今的高效能運算處理器。此高效的設計方式可讓各項功能分散到以不同製程技術生產的個別微小裸晶,提供了靈活性、更好的良率、及節省成本的優勢。小晶片必須能夠透過密集、高速、高頻寬的連結來進行彼此溝通,才能確保最佳的效能水準,為了克服這項挑戰,此小晶片系統採用台積公司所開發的Low-voltage-IN-Package-INterCONnect(LIPINCONTM)獨特技術,資料傳輸速率達8Gb/s/pin,並且擁有優異的功耗效益。

小晶片系統細節說明

此款小晶片系統建置在CoWoS中介層上由雙個7奈米生產的小晶片組成,每一小晶片包含四個Arm Cortex®- A72處理器及一個晶片內建跨核心網狀互連匯流排,小晶片內互連的功耗效益達0.56pJ/bit、頻寬密度為1.6Tb/s/mm2、0.3伏LIPINCON介面速度達8GT/s且頻寬速率為320GB/s。此小晶片系統於2018年十二月完成產品設計定案,並已於2019年四月成功生產。

Arm資深副總裁暨基礎設施事業部總經理 Drew Henry表示:「這次與我們長期夥伴台積電協作的最新概念性驗證成果,結合了台積電創新的先進封裝技術與Arm架構卓越的靈活性及擴充性,為將來生產就緒的基礎架構系統單晶片解決方案奠定了絕佳的基礎。」

台積公司技術發展副總經理侯永清博士表示:「此款展示晶片呈現出我們提供客戶系統整合能力的絕佳表現,台積公司的CoWoS先進封裝技術及LIPINCON互連介面能協助客戶將大尺寸的多核心設計分散到較小的小晶片組,以提供更優異的良率與經濟效益。Arm與台積公司的本次合作更進一步釋放客戶在雲端到邊緣運算的基礎架構應用上高效能系統單晶片設計的創新。」

圖說一:雙小晶片之系統平面圖

Related Semiconductor IP

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- LunaNet AFS LDPC Encoder and Decoder IP Core

Related News

- Flex Logix 基于 TSMC 7nm 技术的 EFLX4K eFPGA IP 内核现已上市

- Socionext宣布与Arm和台积电合作开发基于Chiplet技术的2nm多核CPU芯片

- GUC 宣布成功推出业界首款采用台积电 3nm 和 CoWoS 技术的 UCIe 32G 芯片

- Rambus面向网络和数据中心的微型芯片及共封装光学器件提供112G XSR / USR PHY,此解决方案适用于台积电7nm工艺上