新思科技携手台积公司简化多裸晶系统复杂性,推出面向台积公司N3E工艺的"从架构探索到签核" 统一设计平台和经验证的UCIe IP

广æ³çå¤è£¸æ¶ç³»ç»è®¾è®¡è§£å³æ¹æ¡å¯æ¯æ3Dblox 2.0æ ååå°ç§¯å ¬å¸3DFabricTMææ¯ï¼æé«å¿«éå¼æéæçç产ç

å å©ç¦å°¼äºå·æ¡å°¼ç»´å°2023å¹´11æ8æ¥ -- æ°æç§æï¼Synopsys, Inc., 纳æ¯è¾¾å è¡ç¥¨ä»£ç : SNPSï¼è¿æ¥å®£å¸è¿ä¸æ¥æ©å¤§ä¸å°ç§¯å ¬å¸çåä½ï¼åæ¹æºæéè¿å¯æ¯æææ°3Dblox 2.0æ ååå°ç§¯å ¬å¸3DFabric™ææ¯çå ¨é¢è§£å³æ¹æ¡ä¸æä¼åå¤è£¸æ¶ç³»ç»ï¼Multi-Dieï¼è®¾è®¡ãæ°æç§æå¤è£¸æ¶ç³»ç»è§£å³æ¹æ¡å æ¬ "ä»æ¶ææ¢ç´¢å°ç¾æ ¸"ç»ä¸è®¾è®¡å¹³å°3DIC Compilerï¼å¯æä¾è¡ä¸é¢å ç设计æçï¼æ¥å®ç°è¯çç容éåæ§è½è¦æ±ãæ¤å¤ï¼æ°æç§æ UCIe IPä¹å·²å¨å°ç§¯å ¬å¸é¢å çN3Eå è¿å·¥èºä¸åå¾äºé¦æ¬¡éè¿ç¡ ççæåï¼å®ç°die-to-dieé«éæ ç¼äºè¿ã

å°ç§¯å ¬å¸è®¾è®¡åºç¡è®¾æ½ç®¡çé¨è´è´£äººDan Kochpatcharin表示ï¼"å°ç§¯å ¬å¸é¿æä¸æ°æç§ç´§å¯åä½ï¼ä¸ºè¯çå¼åè æä¾å·®å¼åç解å³æ¹æ¡ï¼å¸®å©ä»ä»¬è§£å³ä»æ©ææ¶æå°å¶é è¿ç¨ä¸é¢ä¸´çé«åº¦å¤æææãæ们ä¸æ°æç§æçé¿æåä½ï¼è®©æ们çå ±å客æ·è½å¤éé对æ§è½ååèæçä¼åç解å³æ¹æ¡ï¼ä»¥åºå¯¹é«æ§è½è®¡ç®ãæ°æ®ä¸å¿å汽车åºç¨é¢åçå¤è£¸æ¶ç³»ç»è®¾è®¡è¦æ±ã"

æ°æç§æEDAäºä¸é¨æç¥ä¸äº§å管çå¯æ»è£Sanjay Bali表示ï¼"æ们ä¸å°ç§¯å ¬å¸å¼ºå¼ºèåï¼ä¸ºå¤è£¸æ¶ç³»ç»æä¾äºå ¨é¢ãå¯æ©å±ç解å³æ¹æ¡ï¼å®ç°äºåææªæçè¯çæ§è½å设计æçãéç¨3Dblox 2.0çéç¨æ åå¨ç»ä¸è®¾è®¡å¹³å°ä¸è¿è¡å¤è£¸æ¶ç³»ç»è®¾è®¡çæ¶ææ¢ç´¢ãåæåç¾æ ¸ï¼å¹¶ç»åå¨å°ç§¯å ¬å¸N3Eå·¥èºä¸å·²å®ç°é¦æ¬¡éè¿ç¡ çæåçæ°æç§æ UCIe PHY IPï¼å®¢æ·è½å¤è¿ä¸æ¥å éä»æ©ææ¶ææ¢ç´¢å°å¶é çç³»ç»è®¾è®¡å ¨æµç¨ã"

æ°æç§æ3DIC Compiler设计平å°å·²éè¿å°ç§¯å ¬å¸è®¤è¯ï¼å¯å¨ç»ä¸ç裸ç/å°è£ æ¢ç´¢ãåå设计ååæå¹³å°ä¸ä½¿ç¨3Dblox 2.0æ åå3DFabricææ¯è¿è¡å ¨æ 设计ãæ°æç§æéæç³»ç»åæåè½å¯ä¸3Dblox 2.0ç³»ç»åå设计ç¸ç»åï¼ååä¼åçåçµæºå®æ´æ§ï¼æå©äºç¡®ä¿è®¾è®¡å¯è¡æ§ãæ°æç§æåAnsysæç»åä½ï¼å°æ°æç§æ 3DIC CompileråAnsyså¤ç©çåæææ¯ç¸éæï¼æä¾ç³»ç»çº§ææçç¾æ ¸åç¡®æ§ãæ°æç§æ3DIC Compilerè¿å¯ä¸æ°æç§ææµè¯äº§åäºæä½ï¼ä»¥ç¡®ä¿æ¹éæµè¯åè´¨éã

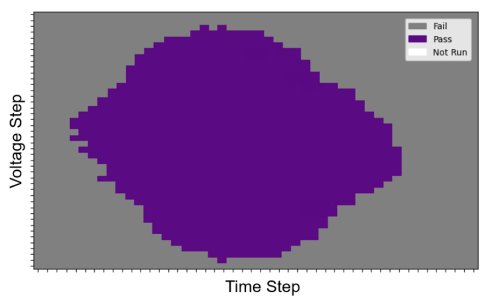

æ°æç§æUCIe PHY IPå·²å¨å°ç§¯å ¬å¸ N3Eå·¥èºä¸å®ç°é¦æ¬¡éè¿ç¡ ççæåï¼å¹¶è·å¤å®¶å ¨çé¢å ä¼ä¸éç¨ï¼è½å¤å¸®å©å¼åè é«æå°å°die-to-dieäºèçä¸çæ åéæå°ä»ä»¬çå¤è£¸æ¶ç³»ç»ä¸ãç»ææ¾ç¤ºï¼è¯¥IPå¨16Gbpsæ¶å¯å®ç°è¡ä¸é¢å çåèæçåæ§è½ï¼å¹¶å¯æ©å±è³24Gbpsï¼åæ¶å ·æ强大çé¾è·¯è£éãæ°æç§æçå®æ´UCIe CompilerãPHYåéªè¯IP解å³æ¹æ¡ç®åå·²æ¯ææ ååå è¿å°è£ ï¼æä¾äºæµè¯ãä¿®å¤åçæµåè½ï¼å³ä½¿å¨ä»¥ç¡®ä¿å¤è£¸æ¶ç³»ç»å¨ç°åºæä½ä¸çå¯é æ§ãæ¤å¤ï¼æ°æç§æè¿æä¾äºé¢åHBM3ææ¯çå®æ´IP解å³æ¹æ¡ï¼ä»¥æ»¡è¶³Multi-Dieç³»ç»çé«å å带宽éæ±ãæ°æç§æIP产åä¸æ°æç§æ3DIC Compilerçç»åéè¿èªå¨åå¸å±å¸çº¿ãä¸ä»å±ç 究åä¿¡å·å®æ´æ§åæï¼æ¯æ3Dblox 2.0 die-to-dieå¯è¡æ§ç 究ï¼ä»èæé«ç产å并éä½IPéæé£é©ã

ä¸å¸æ åµ

- æ°æç§æé¢åå°ç§¯å ¬å¸N3Eå·¥èºçUCIe PHY IPå3DIC Compilerç°å·²ä¸å¸ã

- æ°æç§æé¢åå°ç§¯å ¬å¸å è¿å·¥èºç HBM3 IPç°å·²ä¸å¸ã

æ´å¤èµæºç¹å»

- ç½ç»èµæºï¼ æ°æç§æ Multi-Dieç³»ç»è§£å³æ¹æ¡

- æ°æç§æè¡ä¸æ´å¯æ¥åï¼ Multi-Dieç³»ç»å°å¤å¿«æ¹åå导ä½è®¾è®¡ï¼

- 线ä¸ç 讨ä¼ï¼ Multi-Dieç³»ç»çæåä¹è·¯

- ç½ç»èµæºï¼ é¢åå°ç§¯å ¬å¸ N3E å·¥èºçä¸çå¹¿æ³ IP 产åç»åå®ç°é¦æ¬¡éè¿ç¡ çæå

å ³äºæ°æç§æ

æ°æç§æï¼Synopsys, Inc.ï¼çº³æ¯è¾¾å è¡ç¥¨ä»£ç ï¼SNPSï¼æ¯ä¼å¤åæ°åå ¬å¸çSilicon to Software™ï¼"è¯çå°è½¯ä»¶"ï¼åä½ä¼ä¼´ï¼è¿äºå ¬å¸è´åäºå¼åæ们æ¥å¸¸æä¾èµççµå产åå软件åºç¨ãä½ä¸ºå ¨ç第15å¤§è½¯ä»¶å ¬å¸ï¼æ°æç§æé¿æ以æ¥ä¸ç´æ¯çµå设计èªå¨åï¼EDAï¼åå导ä½IPé¢åçå ¨çé¢å¯¼è ï¼å¹¶ä¸å¨è½¯ä»¶å®å ¨åè´¨é解å³æ¹æ¡æ¹é¢ä¹åæ¥çè¶æ¥è¶å¤§çé¢å¯¼ä½ç¨ãæ 论æ¨æ¯å è¿å导ä½ççä¸ç³»ç»ï¼SoCï¼å¼åè ï¼è¿æ¯ç¼åéè¦æé«å®å ¨æ§åè´¨éçåºç¨ç¨åºç软件å¼åè ï¼æ°æç§æé½è½å¤æä¾æ¨æéè¦ç解å³æ¹æ¡ï¼å¸®å©æ¨æ¨åºåæ°æ§ãé«è´¨éãå®å ¨ç产åãå¦éäºè§£æ´å¤ä¿¡æ¯ï¼è¯·è®¿é®www.synopsys.com/zh-cn

Related Semiconductor IP

- UCIe RX Interface

- AXI-S Protocol Layer for UCIe

- UCIe PHY (Die-to-Die) IP

- UCIe Controller baseline for Streaming Protocols for ASIL B Compliant, AEC-Q100 Grade 2

- UCIe D2D Adapter

Related News

- 新思科技推出业界首个统一平台3DIC Compiler,以加速多裸晶芯片系统设计和集成

- 新思科技3DIC Compiler通过三星多裸晶芯片集成流程认证,助力2.5D和3D IC设计

- 新思科技EDA和IP完整解决方案获台积公司N3E工艺认证,加速HPC、AI、和移动领域设计

- 新思科技面向台积公司先进技术推出多裸晶芯片设计解决方案,共同推动系统级创新