芯来科技发布UX1030H,全面支持RVA23

2025年6月24日,上海 —— 在RISC-V生态持续推进标准化、高性能发展的背景下,国内对具备虚拟化能力、安全隔离机制及高并发处理能力的处理器需求显著增长。今日,芯来科技(Nuclei System Technology)正式发布其新一代高性能处理器IP —— UX1030H。

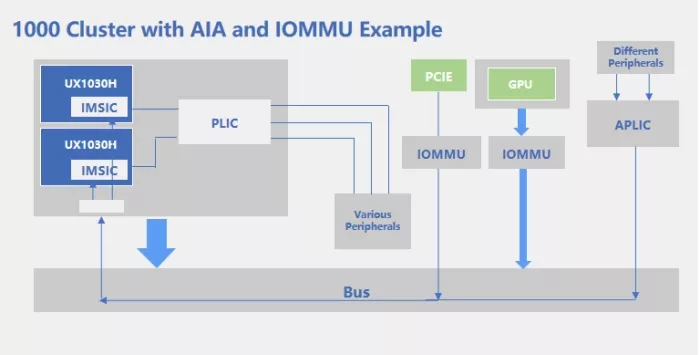

该产品严格遵循RVA23 Profile规范,全面支持虚拟化及向量计算扩展,并在此基础上进一步提供对IOMMU和AIA(Advanced Interrupt Architecture)的支持,面向新一代高安全、高扩展性的应用场景,标志着国产RISC-V高性能处理器IP在生态融合与系统适配能力上迈出关键一步。

RISC-V生态加速,IP化成关键

作为全球唯一开放、可扩展的主流指令集架构,RISC-V正快速向工业规模化应用扩展。其开放性与模块化特性,使其成为推动芯片自主化和架构创新的重要力量。

在这一进程中,高质量RISC-V处理器IP的产业化成为落地的关键环节。它不仅是芯片流片和量产的技术基础,也决定了操作系统兼容性与生态完整性。

据SHD Group预测,到2031年,全球基于RISC-V的SoC芯片出货量将达到200亿颗,占全球市场份额的25%。RISC-V IP正从控制类应用加速迈向边缘计算、智能网关、AI推理等高性能场景,对稳定、标准、可扩展的CPU IP提出更高要求。

在这一背景下,高性能、生态友好的RISC-V IP产品将成为推动产业突破的关键支撑。

高性能RISC-V需求快速上升

过去几年,RISC-V架构在中低功耗处理器市场快速落地,特别是在对标Arm Cortex-A53/A55级别的通用计算场景中,已实现从产品化到规模化部署。当前,RISC-V CPU IP在智能终端、边缘网关、低功耗AI等领域形成了较为成熟的生态与工具支持,此级别的处理器的典型代表是芯来科技的UX900系列处理器IP。

在此基础上,市场正加速迈向对标Cortex-A72级别的中高端RISC-V处理器IP需求阶段,典型应用主要包括:

- 边缘AI计算与语义识别引擎

- 智能汽车域控制器与车载虚拟化平台

- 高性能边缘服务器与工业智能设备

- 多核异构SoC中的主控核心或虚拟化运行环境

借助RISC-V Vector扩展标准,RISC-V在AI推理与并行计算场景中展现出更高的灵活性与性能潜力。当前正是RISC-V从“控制类芯核”向“主控级通用处理器”升级的关键节点,具备标准化、商用能力和生态兼容性的高性能RISC-V处理器IP,将成为推动下一阶段产业突破的核心力量。

严格支持RVA23,生态性能兼顾

芯来科技推出的UX1030H处理器IP,严格遵循RVA23 Profile规范,兼顾生态完整性与高性能演进,是RISC-V高端应用领域的重要基础组件。

RVA23 Profile是RISC-V软件生态面向64位高性能通用处理器场景的重要标准,明确要求处理器必须支持包括Hypervisor和Vector在内的关键扩展。UX1030H完全符合RVA23规范,具备运行通用操作系统与虚拟化环境的能力,并可无缝对接RISC-V日益成熟的开放软件生态体系。

特别值得强调的是,RVA23已被明确作为未来主流RISC-V平台运行Android操作系统的基本架构基线,包括Google、Red Hat、Canonical等关键厂商正在围绕RVA23构建下一阶段的系统软件支持。RVA23的标准化正在成为RISC-V生态突破桌面级和移动级平台的重要起点。

在此基础上,UX1030H额外提供:

- IOMMU支持:实现外设访问隔离与内存管理能力,增强系统安全性与资源隔离能力。

- AIA支持:为RISC-V系统提供高性能、可扩展且支持虚拟化的中断处理框架,显著优化多核与虚拟化场景下的中断效率和灵活性

该组合能力使UX1030H不仅满足RVA23软件栈的基本运行要求,也具备支撑复杂虚拟化系统、高可靠设备接入和高并发中断调度的硬件能力,为Android在RISC-V架构上的广泛部署打下坚实基础。

架构升级,延续UX1000优势

UX1030H基于芯来科技自研的UX1000系列微架构平台,在原有成熟设计的基础上,进一步增强计算性能、并行能力和可扩展性,面向高性能RISC-V处理器的实际部署场景。

该处理器采用3译码宽度乱序执行架构,具备深度流水线设计,面向高负载、密集调度场景,提供出色的单核性能与执行效率。微架构内核可灵活配置性能参数,兼顾不同SoC平台对算力、功耗、面积的平衡要求。

- 12级乱序执行流水线,支持复杂指令调度与乱序重排,提高指令吞吐效率

- 每周期最大支持6条标量指令与2条矢量指令并行发射,释放计算资源

- 全面支持RISC-V Vector 1.0标准,并可配置最高256位(VLEN=DLEN=256)的向量处理能力,适用于AI推理、图像处理、信号分析等计算密集型场景

- 支持L1 I/D Cache、ILM/DLM片上内存配置、Cluster Cache

此外,UX1030H支持多核扩展架构,单个Cluster最多可配置16个核心,并支持多级缓存一致性机制,适用于面向高并发、高吞吐量系统的集群化部署需求。该设计为处理器在数据中心加速卡、智能汽车控制器及高性能边缘平台中的集成使用提供了可靠基础。

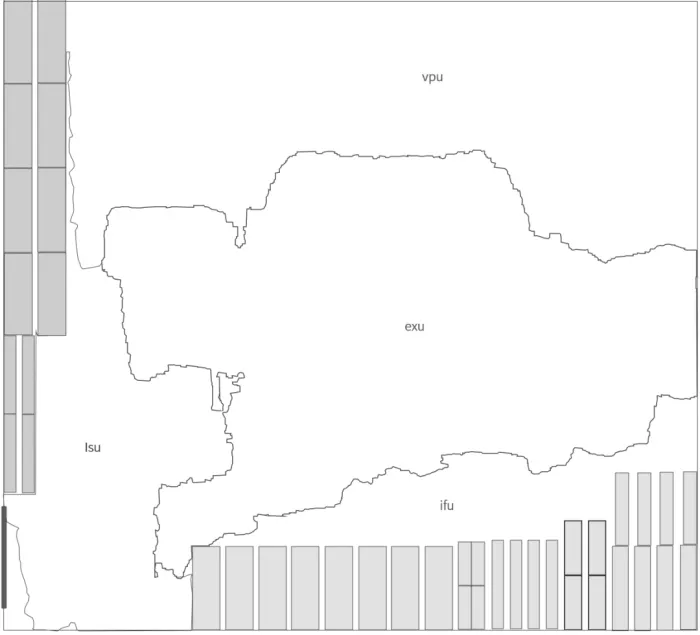

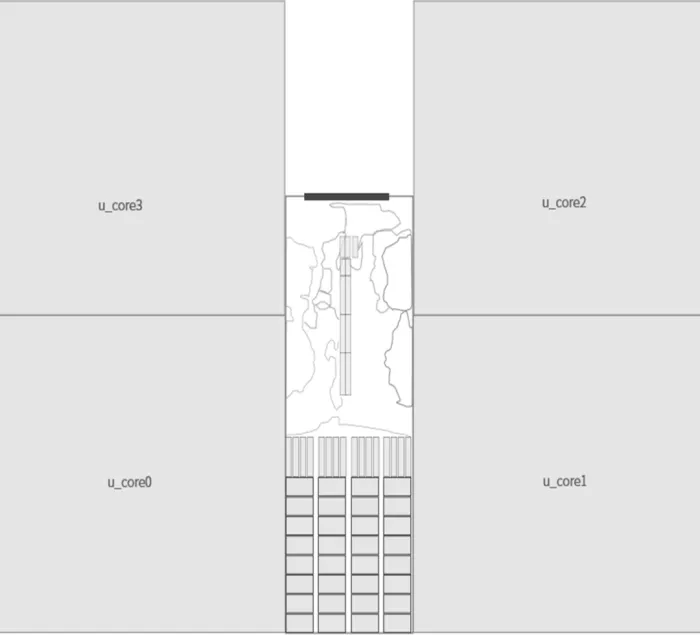

目前,UX1030H已进入客户导入阶段,多个合作项目正在进行SoC集成验证与平台适配。在T22工艺下可达1.6GHz。以下为UX1030H典型配置下的Floorplan示意图,展示其在面积优化与功能集成方面的布局特性。

单核FloorPlan

四核Cluster Floorplan

标准指令,跑分性能领先

在RISC-V CPU IP市场中,性能评估的准确性和可比性是客户决策的重要参考。

在当前典型配置下,UX1030H核心取得如下性能表现:

- 在遵循Dhrystone Ground Rule,不启用内联优化(编译选项 -fno-inline)的前提下,Dhrystone跑分达到5.35 DMIPS/MHz;

- CoreMark跑分达到8.5 CoreMark /MHz

注意:芯来科技在UX1030H的性能测试中,坚持采用完整标准RISC-V指令集进行编译与执行,未引入任何自定义指令刻意提升跑分,确保性能结果具有开放性、公平性与平台可迁移性。

该成绩在同类RISC-V高性能内核中处于领先水平,充分体现出UX1030H在指令调度、执行通道、Cache体系与流水线深度设计上的综合优化能力。

相较于部分依赖自定义指令集扩展以提升理论跑分的RISC-V处理器方案,UX1030H在标准RISC-V规范之内实现高性能输出,更利于后续操作系统、编译器、库文件等软件生态的直接兼容和长期维护。

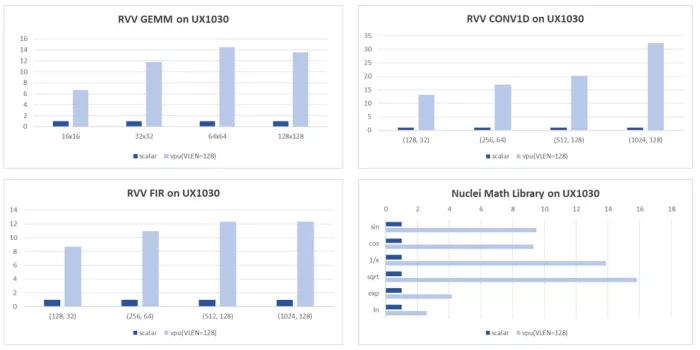

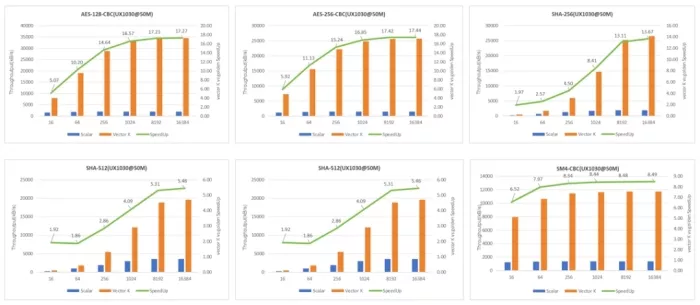

同时,UX1030H内建的VPU(矢量处理单元)在图像计算、张量运算、加密等负载下提供了显著的性能加速能力。

独特特性,具备创新设计

UX1030H在延续UX1000系列微架构可扩展性优势的基础上,集成了多项系统级功能特性,进一步提升处理器在复杂SoC系统中的集成能力与实际应用效率,适配虚拟化、高吞吐外设访问、实时处理等关键需求场景。

支持双运行模式

UX1030H支持Linux通用操作系统运行模式与实时处理模式双模式运行配置,可在不同应用场景下灵活切换处理器特性,满足控制类任务的低延迟响应需求,同时也适配完整的操作系统和应用软件栈,适用于智能边缘、工业控制、车载计算等多样化场景。

支持Cluster Local Memory(CLM)

UX1030H支持将集群缓存配置为Cluster Local Memory(CLM),并提供CLM接口,供集群内多个核心或其他计算模块共享访问,提供更强的实时计算能力。

CLM设计适配SoC中典型的AI协处理器、图像引擎、DSP模块等场景下的片上数据共享需求。

可配置IO一致性接口(IOCP)

UX1030H提供可配置的IO一致性接口(IOCP),用于支持系统中多个外部主设备与处理器之间的数据一致性共享:

- 支持外部 Master(如 NPU、加速器、PCIe 控制器、DMA 等)访问处理器Core和Cluster Cache

- 在不需软件干预的情况下保持缓存数据一致性

- 降低I/O访问延迟,提高异构系统的整体带宽与响应性能

软件生态稳步成熟,全球协同共建

RISC-V作为开放指令集,其软件生态正在快速完善,从工具链、编译器到操作系统、虚拟化和中间件,已逐步形成面向高性能应用的完整基础设施。LLVM、GCC、glibc、Linux内核、QEMU等主流组件均已实现长期主线支持,Android、Debian、OpenEuler等操作系统也陆续完成对RVA Profile的适配。

RVA23的推出,为RISC-V运行大型操作系统如 Android 提供了统一的软件架构基础,Google、Red Hat、Canonical等国际厂商已全面参与相关开发,RISC-V软件生态正迈入以标准兼容性与平台稳定性为核心的新阶段。

芯来科技持续投入RISC-V软件栈建设,围绕UX系列处理器提供完善的开发工具与操作系统适配支持,包括GNU工具链、GDB、开源SDK、驱动模板及RTOS/Linux验证工程,并积极参与 OpenEuler、Android on RISC-V 等开源项目。

得益于标准指令集架构(没有引入自定义私有指令集)与全栈工具支持,UX1030H具备优良的软件兼容性与快速集成能力,帮助客户在不同平台上高效部署应用系统。

芯来科技创始人胡振波表示:

UX1030H的发布是芯来科技在RISC-V高性能处理器IP路线上的又一关键里程碑。作为全球最早可获得的、严格支持RVA23 Profile的高性能RISC-V CPU IP之一,它不仅符合最新生态规范,也具备出色的系统级特性,体现了我们对开放架构未来的坚定投入。

2025年是芯来科技成立第七周年。自2018年起,我们始终坚持自主研发、市场驱动,逐步成长为本土RISC-V CPU IP领域的代表性企业,构建了覆盖32位到64位、通用与专用并行发展的产品体系。

截至目前,我们已服务超过300家客户,建立起本土市场中产品线最完整、客户覆盖最广的交付能力。

面向未来,我们将持续深耕高性能、低功耗、安全计算等关键技术,打造智能计算核心,为RISC-V生态繁荣与国产芯片产业发展持续注入动力。

强化国产自主IP供给,拓展高端产品谱系

UX1030H的推出,进一步夯实了芯来科技在RISC-V CPU IP产品线上的高端布局,强化国产自主IP供给,助力软件生态向通用计算平台快速迁移。

未来,芯来科技将继续围绕通用处理、智能计算、安全隔离与虚拟化等方向推进产品演进,构建更完整、更具深度的RISC-V处理器生态,推动本土算力平台向高性能持续跃升。