Dolphin Integration 宣布其RISC-V子系统:RV32 Tornado的可用性

Meylan, France - May 28, 2018 -- Dolphin Integration, a major leader in energy-efficient IPs, announces the availability of its RISC-V subsystem called RV32 Tornado.

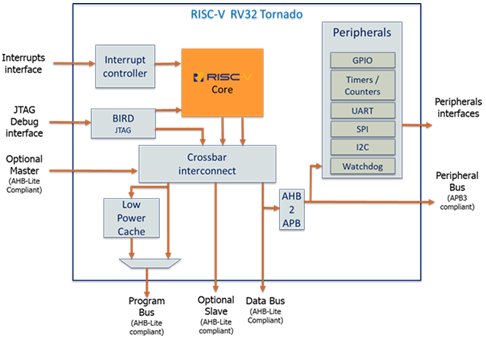

This MCU subsystem has been designed to fit the IoT requirements in terms of area and low-power consumption. It is fully configurable to enable a fast design-in and fast time-to-market. The RV32 Tornado subsystem embeds:

- an adapted version of thePULP zero-riscy core from ETH-Zurich

- a typical set of peripherals: GPIO, UART, SPI, I2C, Timers and watchdog

- standard AHB/APB interfaces

- an ultra-low power cache controller

- a debug unit with JTAG interface integrating advanced features

The RISC-V subsystem comes with a powerful software development and debug tool, an IDE called SmartVisionTM. It is an open environment allowing the design of complete subsystems based on processor cores and peripherals. SmartVisionTM provides an intuitive interface as well as the necessary tools to develop and debug embedded software by simulation or by In Circuit Emulation.

For more information, please contact us at contact@dolphin.fr or on our website: www.dolpin-integration.com

About Dolphin Integration

Dolphin Integration is a pioneer in Energy-Efficient Systems-on-Chip enablement. The company serves a growing range of applications from battery-operated to line-powered. Its portfolio of more than 200 silicon IPs covering Foundation, Feature and power Fabric IPs are proven and available in multiple processes and foundries. This coherent portfolio allows to reduce SoC power consumption in sleep, triggering and active processing modes. The company is committed to its customer success through constant innovation, quality control and dedicated support. Dolphin Integration comes with 30 years experience in integration of silicon IP components leveraging power-integrity driven simulation tools to design and supply cost-effective logic and mixed-signal ASIC/SoC.

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- 海豚集成基于台积电55 ULP / ULP-Ef制程的低功耗标准单元库SESAME eLV library

- 尝试海豚集成(Dolphin Integration)的MIWOK,语音检测器的设计基准

- 海豚集成的服务和ASIC/SoC集成业务获得EN 9100认证

- Dolphin Integration 180纳米标准单元库帮助RFID芯片大幅提高功耗和密度性能