video interface IP

Filter

Compare

530

IP

from

90

vendors

(1

-

10)

-

General Video Interface HS Receiver PHY

- General Video Interface HS Receiver PHY IP

- Next generation HD interface with low EMI

- Fully comply with V-By-One HS V1.3 electrical specification

- Low power consumption for multiple lane application

-

General Video Interface HS Transmitter PHY

- Next generation HD interface with low EMI

- Fully comply with V-By-One HS V1.3 electrical specification

- 0.45Gbps to 3Gbps continues data rate range

- Compatible with both CML and LVDS topology

-

Camera/HDMI Video Input Interface

- 444 RGB/YCbCr from HDMI or 422 YCbCr from Digital camera

- 24-bit pixel data from HDMI or 8-bit pixel data from Digital camera

- Supports Progressive type scan

- Programmable resolution up to 1080p

-

Video Decoder Interface

- Supports BT601 interface

- Supports BT656 interface

- Supports both NTSC & PAL resolution

- Programmable polarity of frame clock & line clock

-

Video Encoder Interface

- Parallel interface support for 10-bit

- Programmable polarity of frame clock & line clock

- YCbCr 4:2:2 data

- Supports interlace type scan

-

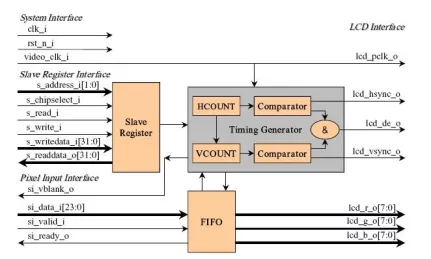

LCD/HDMI Video Output Interface

- Display modes

- Supports programmable display size

- Supports progressive type of displays

- Programmable pixel clock frequency

-

Digital Video Broadcast - Asynchronous Serial Interface

- Compatible with DVB standard

- 310/270 Mbit Asynchronous

- deserializer

- Robust Jitter tolerance

-

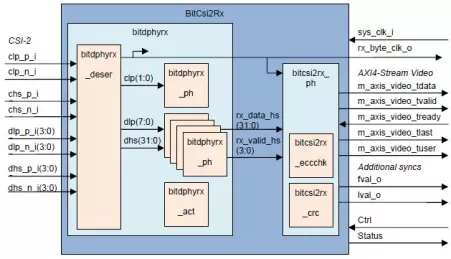

Very compact (500 LUTs) Camera Sensor Receiver Interface Converting from MIPI CSI-2 to AXI4-Stream Video Standard

- 1 to 4 data lanes

- Number of data lanes can be configured statically at synthesis time and dynamically during run-time

-

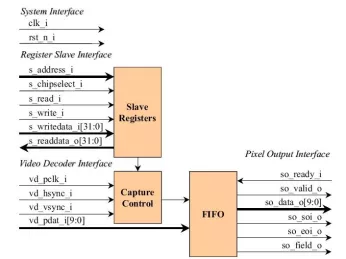

Digital Camera Interface

- Supports image and video capturing of DVP interface camera (GC0308/OV5640)

- Supports image and video capturing of parallel digital video decode chip (TVP5150)

- Supports 8-, 10-, 12-, 14-, 16-bit parallel input data

-

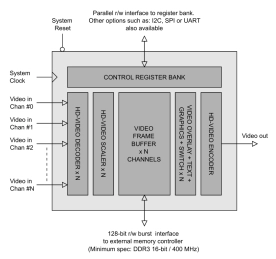

HD Multi-window Video Processor IP Core

- This brief specification describes the operation of the HD Multi-window Video Processor (evaluation) IP Core.

- The IP Core is provided as a netlist in either EDIF, Verilog or VHDL formats.