ultra-low power register file IP

Filter

Compare

8

IP

from

4

vendors

(1

-

8)

-

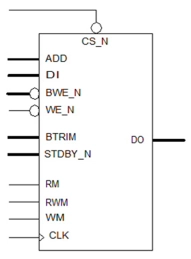

Low Power Memory Compiler - 1-Port Register File Compiler - GF 22nm FDX

- Specifically designed for ultra-low power applications, this memory leverages body biasing to dramatically reduce power consumption.

- Compatible with industry Adaptive Body Biasing IP for PVT and aging compensation

- Body Biasing functionality (up to +1.3V / -1.5V) to reduce leakage or increase speed at the same power

-

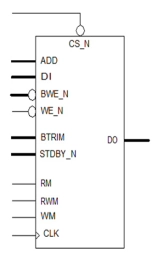

Single Port Low Leakage Register File Compiler - GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage.

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (L110) bit cells to ensure high manufacturing yields.

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

Single Port Low Leakage Register File Compiler - GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

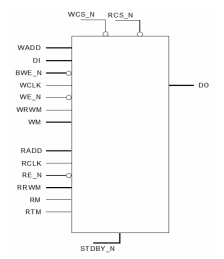

Dual Port (1 read only port, 1 write only port) Register File Compiler on N22ULL

- Ultra-Low Leakage: High VT (HVT) are used to minimize leakage performance.

- Bit Cell: Utilizes Foundries 8T bit cells to ensure high manufacturing yields

- Deep Sleep Mode Retains data a minimal power consumption.

-

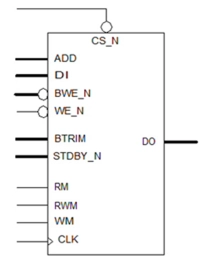

Single Port Register File Compiler on N22ULL

- Ultra-Low Leakage: High VT (HVT) are used to minimize leakage performance.

- Bit Cell: Utilizes Foundry’s 6T bit cells to ensure high manufacturing yields

- Deep Sleep Mode Retains data a minimal power consumption. Dedicated standby mode reduces power required to an absolute minimum to retain the memory contents.

-

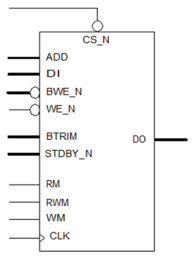

Single Port Low Leakage Register File Compiler - GF 22FDX

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

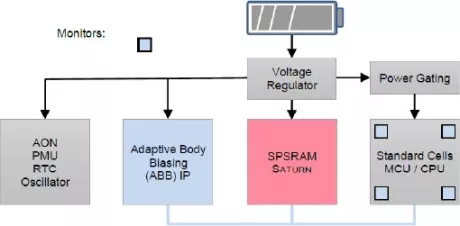

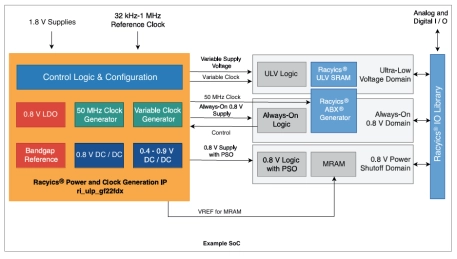

Power and Clock Generation IP - GLOBALFOUNDRIES® 22FDX®

- Tightly integrated power management platform with a soft-IP wrapper around Analog / Mixed-Signal hard macros which generate all supply voltages and clock signals needed to run highly efficient SoCs in GlobalFoundries® 22FDX®.

- Running from only one supply voltage and reference clock, the IP generates its own internal supplies and references, and those needed to run the Racyics® ABX® Generator.

-

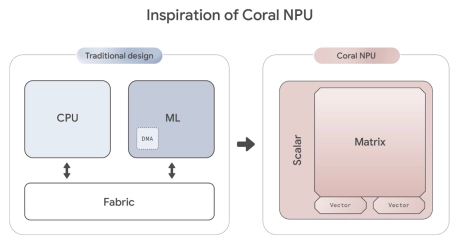

RISC-V-Based, Open Source AI Accelerator for the Edge

- Coral NPU is a machine learning (ML) accelerator core designed for energy-efficient AI at the edge.

- Based on the open hardware RISC-V ISA, it is available as validated open source IP, for commercial silicon integration.