eFPGA IP

Filter

Compare

8

IP

from

6

vendors

(1

-

8)

-

eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

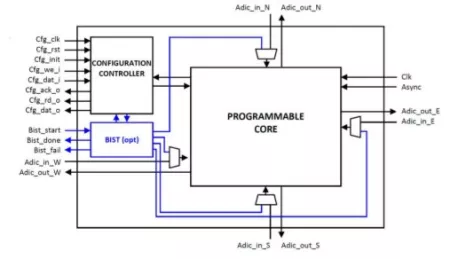

- RapidFlex eFPGA IP provides a reconfigurable, upgradeable, and iterative logic computing layer for SoCs, MCUs, AI accelerators, industrial control, and communication chips.

- Based on RapidFlex's self-developed ArkAngel® toolchain (AAEE), our eFPGA core delivers full-flow capabilities from architecture exploration → RTL → physical implementation (GDSII) → digital design flow verification, leading the industry in performance density, integrability, and toolchain experience.

-

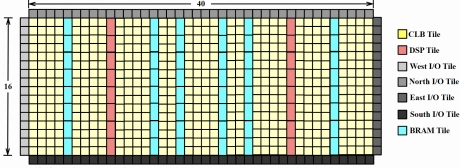

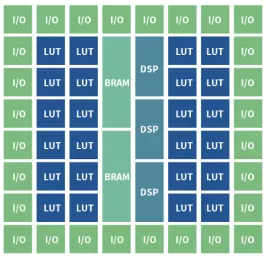

Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- An experimental Z1010 heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs has been ported to the GlobalFoundries GF12LP process.

- The picture below shows the full layout of the experimental architecture. The official Z1010 standard will include a different ratio of LUTs, DSPs, and BRAM.

-

eFPGA on GlobalFoundries GF12LP

- All Platypus eFPGA hardened IP cores are backed up by an open architecture guarantee. Complete machine readable descriptions of standard architectures can be found in the Logiklib open source repository.

- The Z1000 standard eFPGA architecture has been ported to the GlobalFoundries GF12LP process.

-

eFPGA Hard IP Generator

- Combination of over 30 years of programmable logic experience and expertise with proven standard ASIC design methodologies to create an eFPGA IP generator that can create and deliver a domain-specific eFPGA IP in as little as four weeks.

-

Radiation-Hardened eFPGA

- Radiation-Hardened by Design (RHBD): Built to operate in space and defense applications, ensuring reliability under extreme conditions.

- Customizable eFPGA IP: Tailored to specific mission requirements with adaptability to various process nodes and foundries.

- High Reliability: Designed to withstand Total Ionizing Dose (TID) and Single Event Effects (SEE).

-

eFPGA Soft IP

- These eFPGA IP cores offer designers the flexibility to tailor resources to their application requirements, available as either Soft RTL or Hard GDSII IP.

- Our standard-cell-based approach facilitates rapid porting to new process geometries or variants, including industrial and rad-hard grade versions.

-

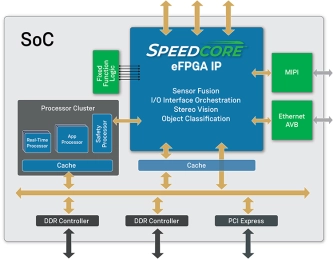

Embedded FPGA

- Speedcore embedded FPGA (eFPGA) IP has brought the performance and flexibility of programmable logic to ASICs and SoCs.

- Customers can integrate a Speedcore eFPGA IP into an ASIC or SoC for high-performance, compute-intensive and real-time processing applications such as artificial intelligence (AI), machine learning (ML), 5G wireless, networking, storage and automotive.

-

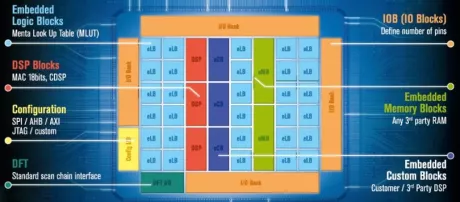

Embedded FPGA

- Fully integrated into RTL SOC design flow

- Highly scalable and customizable

- Technology independent