cJTAG IP

Filter

Compare

26

IP

from

6

vendors

(1

-

10)

-

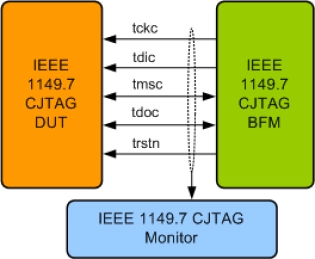

CJTAG (IEEE 1149.7) Verification IP

- Fully compatible with IEEE 1149.7 standard.

- Can be used as TAP controller (slave) or TAP instruction/data generator (Master) for CJTAG.

- Comes with CJTAG monitor to check and report any protocol violation.

- Supports TAP.7 capability classes T0 to T5

-

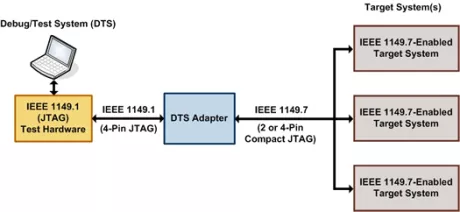

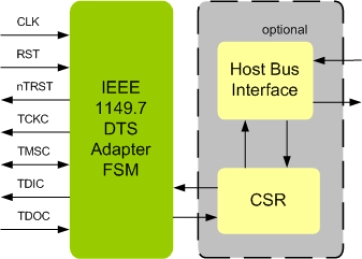

cjTAG IEEE 1149.7 DTS Adapter

- IEEE 1149.1 interface to existing test/debug hardware

- IEEE 1149.7 interface to target system(s)

- Supports all IEEE 1149.7 scan formats

- Supports all IEEE 1149.7 scan topologies

-

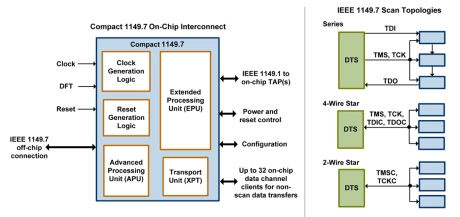

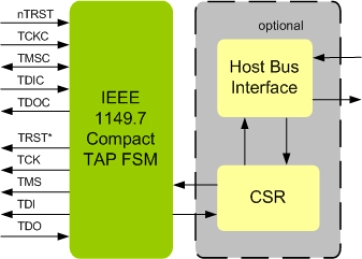

cjTAG IEEE 1149.7 Compact TAP Controller

- Supports IEEE 1149.7 classes 0–5 (selected through hardware configuration parameter)

- Partitioned along IEEE 1149.7-specified functional boundaries (so that only the required hardware is included):

- Supports all mandatory and optional scan formats: JScan0–3, SScan0–3, OScan0–7, and MScan

- Supports all mandatory and optional cJTAG commands

-

IEEE 1149.7 DTS ADAPTER IIP

- Compliant with IEEE 1149.7 standard specification.

- Full IEEE 1149.7 DTS Adapter functionality.

- Supports IEEE 1149.7 classes T0 to T5.

- Supports Reset and Escape sequences generation of TAP controller.

-

IEEE 1149.7 COMPACT TAP IIP

- Compliant with IEEE 1149.7 standard specification.

- Supports TAP.7 capability classes T0 to T5.

- Supports Reset and Selection Unit (RSU) for class T0 optional features.

- Supports Extended Protocol Unit (EPU) for classes T0 to T3.

-

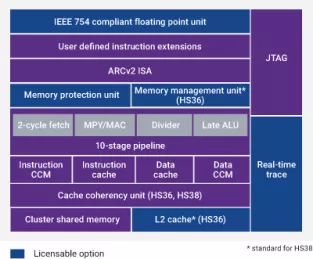

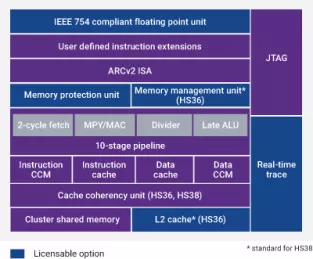

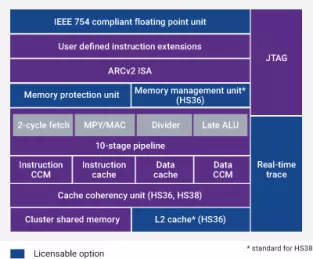

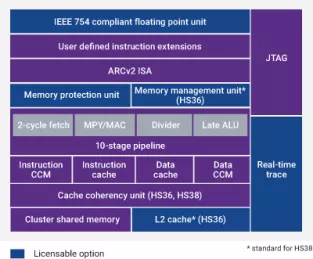

The FastMath Pack is a math processing accelerator for the ARC HS family

- Achieves up to 3232 DMIPS and 6681 CoreMarks* at 1.61 GHz on 28HPM (single-core configuration, worst case silicon and conditions)

- Delivers 2.13 DMIPS/MHz, 4.15 CoreMarks/MHz* (per core)

- High-speed, 10-stage pipeline

- Up to 16MB instruction and data close coupled memory (CCM)

-

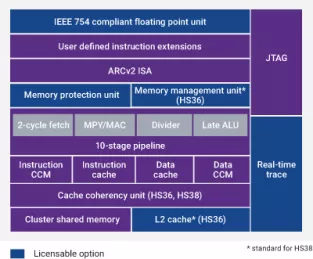

L2 cache option for multicore versions of ARC HS36 and HS38 processors

- Achieves up to 3232 DMIPS and 6681 CoreMarks* at 1.61 GHz on 28HPM (single-core configuration, worst case silicon and conditions)

- Delivers 2.13 DMIPS/MHz, 4.15 CoreMarks/MHz* (per core)

- High-speed, 10-stage pipeline

- Up to 16MB instruction and data close coupled memory (CCM)

-

ARC HS38x4 quad-core 32-bit processor with MMU, ARCv2 ISA, for embedded Linux applications

- Achieves up to 3232 DMIPS and 6681 CoreMarks* at 1.61 GHz on 28HPM (single-core configuration, worst case silicon and conditions)

- Delivers 2.13 DMIPS/MHz, 4.15 CoreMarks/MHz* (per core)

- High-speed, 10-stage pipeline

- Up to 16MB instruction and data close coupled memory (CCM)

-

ARC HS38x2 dual-core 32-bit processor with MMU, ARCv2 ISA, for embedded Linux applications

- Achieves up to 3232 DMIPS and 6681 CoreMarks* at 1.61 GHz on 28HPM (single-core configuration, worst case silicon and conditions)

- Delivers 2.13 DMIPS/MHz, 4.15 CoreMarks/MHz* (per core)

- High-speed, 10-stage pipeline

- Up to 16MB instruction and data close coupled memory (CCM)

-

ARC HS38 32-bit processor with MMU, ARCv2 ISA, for embedded Linux applications

- Achieves up to 3232 DMIPS and 6681 CoreMarks* at 1.61 GHz on 28HPM (single-core configuration, worst case silicon and conditions)

- Delivers 2.13 DMIPS/MHz, 4.15 CoreMarks/MHz* (per core)

- High-speed, 10-stage pipeline

- Up to 16MB instruction and data close coupled memory (CCM)