Wireless Packet Processor IP

Filter

Compare

7

IP

from

5

vendors

(1

-

7)

-

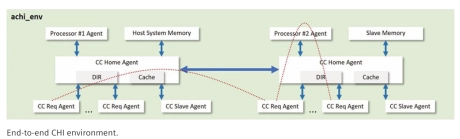

Verification IP for AMBA

- AMBA® ACE and CHI coherent interconnect technologies enable an entirely new class of high-performance datacenter applications in areas of machine learning, network processing, storage off-load, in-memory database, and 4G/5G wireless technology.

- Processor architectures and accelerators can now seamlessly operate over cache coherent intercon nects using the right combination of general-purpose processors and heterogeneous acceleration devices, such as FPGAs, GPUs, network/ storage adapters, intelligent networks, and custom ASICs.

-

IEEE 1588 Boundary, Slave And Master Clock

- Standalone IEEE1588v2 standard compliant BC and Master/Slave OC chip on FPGA

- Hybrid 1588/SyncE mode support

-

IEEE 1588 Boundary, Slave And Master Clock

- Standalone IEEE 1588 v2 standard compliant Boundary Clock (BC) and Ordinary Clock (OC) Master/Slave IP core for Xilinx Spartan-6

- Excellent synchronization performance over most extreme packet transport network conditions

- Slave meets 3G, 4G-LTE and 5G synchronization requirements

- Adaptive to network impairments

-

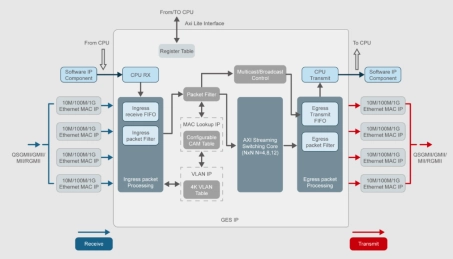

Lithe Layer 2 Gigabit Ethernet Switching IP

- The Lithe Layer 2 Gigabit Ethernet Switching IP is a comprehensive solution for building scalable and efficient network infrastructures.

- Designed to operate at the data link layer of the OSI model, our Lithe Layer 2 IP offers advanced networking capabilities for local area networks (LANs), metropolitan area networks (MANs), and wide area networks (WANs).

- With support for various networking protocols and features, our Lithe IP enables seamless connectivity, reliable data transmission, and efficient network management.

-

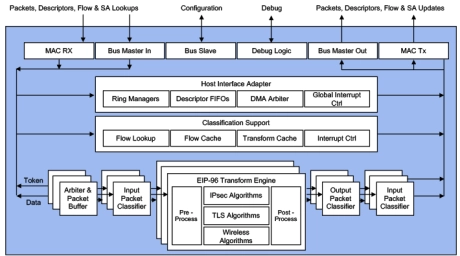

Multi-Protocol Engine with Classifier, Look-Aside, 5-10 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP and MACsec Packet Engine with virtualization, caches classifier and Look-Aside interface for multi-core application processors

- 5-10 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP, DPDK, Linux Crypto

-

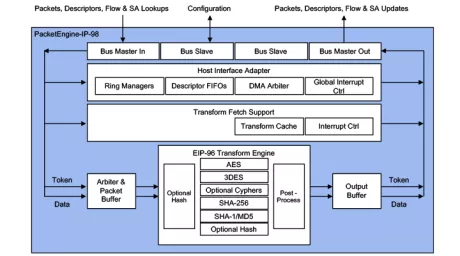

Multi-Protocol Engine with Classifier, Inline and Look-Aside, 10-100 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP, MACsec packet engine with classifier and in-line interface for multi-core server processors

- 10-100 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, streaming and AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP.