Video Analytics IP

Filter

Compare

5

IP

from

4

vendors

(1

-

5)

-

Video Decoder - AV1, HEVC, AVC, VP9

- YUV420 decoding

- 8-/10-bit depth

- I/P/B-frame

- Frame buffer compression

- Multi-instances

- Color space conversion

-

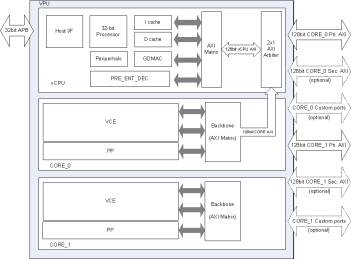

Dual-core video codec - AV1, HEVC, AVC, VP9 (VP9: Decoder only)

- 8/10-bit depth

- I/P/B-frame

- Frame buffer compression

- Multi-instances

- 3rd-party interface (option)

-

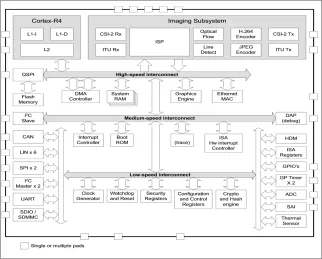

Image Signal Processor (5MP, 2X Sensors) IP

- Self-contained, no external memory needed

- ARM® Cortex-R4 CPU @500 MHz

- Up to 2 Mbytes of SRAM

- Up to 4 Mbytes of stacked Flash or 16 Mbyte external Flash with update via communication interfaces

-

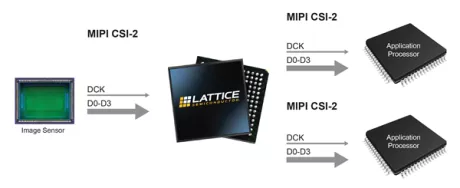

One Input to Two Output MIPI CSI-2 Camera Splitter Bridge

- Supports MIPI CSI-2 up to 6 Gbps per MIPI D-PHY: 1, 2 or 4 data lanes

- Provides one or two MIPI CSI-2 outputs: MIPI CSI-2 data replicated to each output port

- Supports all MIPI CSI-2 data types: RAW, YUV, RGB, User Defined

- Compliance with MIPI D-PHY Specification v1.1

-

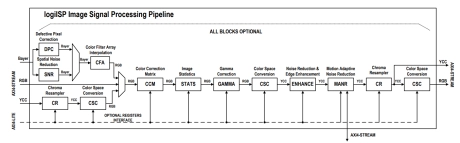

UHD Image Signal Processing (ISP) Pipeline

- The logiISP-UHD Image Signal Processing Pipeline IP core is an Ultra High Definition (UHD) ISP pipeline designed for digital processing and image quality enhancements of an input video stream in Smarter Vision embedded designs based on Xilinx ACAP, MPSoC, SoC and FPGA devices.

- It enables parallel processing of multiple Ultra HD video inputs in different programmable devices, ranging from the small Xilinx Artix®-7 FPGAs to the latest Xilinx Versal Adaptive Compute Acceleration Platform (ACAP) devices.