V-by-One IP

Filter

Compare

30

IP

from

11

vendors

(1

-

10)

-

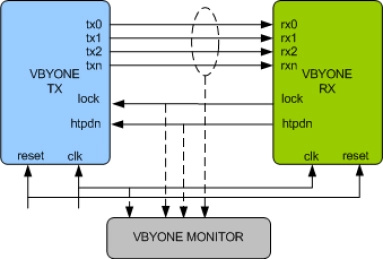

VBYONE Verification IP

- Follows VByOne specification as v1.2/1.3/1.4/1.5

- Support transmitter and Receiver Mode.

- Supports upto 32 serial lanes.

- Supports all byte lengths, color depths, and resolutions.

-

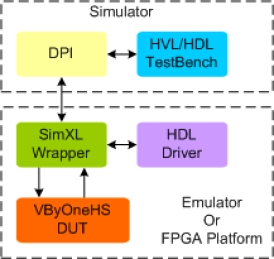

VBYONE Synthesizable Transactor

- Follows VByOne specification as 1.2/1.3/1.4/1.5

- Support transmitter and Receiver Mode

- Supports upto 32 serial lanes

- Supports all byte lengths, color depths, and resolutions

-

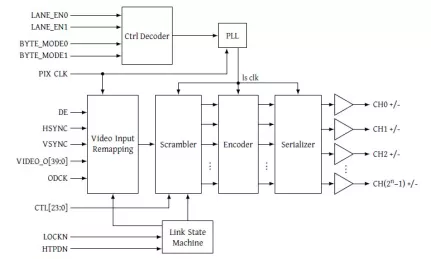

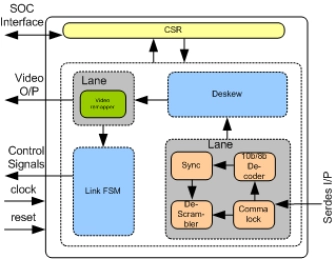

V-By-One Transmitter IIP

- Compliant with VByOne specification 1.2/1.3/1.4.

- Full VBYONE Transmit functionality.

- Supports 1 to 8 lanes. If needed, we can support custom lane configuration.

- Supports all byte lengths.

-

V-By-One Receiver IIP

- Compliant with VByOne specification 1.2/1.3/1.4.

- Full VBYONE Receive functionality.

- Supports 1 to 8 lanes. If needed, we can support custom lane configuration.

- Supports all byte lengths.

-

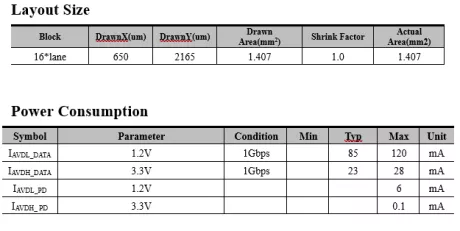

V-by-One Rx IP, Silicon Proven in 40G

- Wide-range data rate, up to 1Gbps, and the associated clock is DDR clock (1/2 of the data rate, up to 500MHz)

- 16 channels total 128 bits of parallel data, each channel has a bit width of 8 bits

- DC coupling mode

- Multi-channel shared offset

-

V-by-One Tx IP, Silicon Proven in 40G

- Wide-range data rate, up to 1Gbps, the associated

- clock is DDR clock (1/2 of the data rate, up to 500MHz)

- 16 channels total 128 bits of parallel data, each channel has a bit width of 8 bits

- DC coupling mode

-

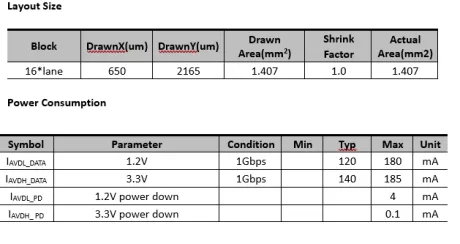

V-by-One Rx IP, Silicon Proven in SMIC 40LL

- Wide-range data rate, up to 1Gbps, and the associated clock is DDR clock (1/2 of the data rate, up to 500MHz)

- 16 channels total 128 bits of parallel data, each channel has a bit width of 8 bits

- DC coupling mode

- Multi-channel shared offset

-

V-by-One Tx IP, Silicon Proven in SMIC 40LL

- 16 channels total 128 bits of parallel data, each channel has a bit width of 8 bits

- DC coupling mode

- Multi-channel shared offset

- Built-in transmitter terminal impedance, no need for off-chip components

-

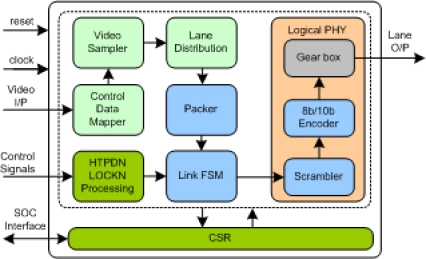

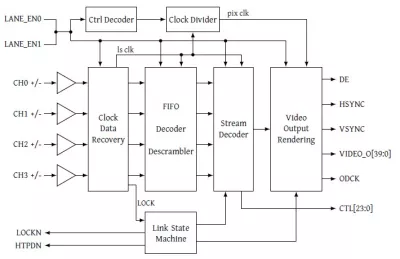

V-by-One 1.4 Receiver

- Compliant with V-by-One 1.4 specification

- Support for up to 4 channels, with up to 4 Gbps data rate per channel

- CDR support to resolve skew problems between clock and data in conventional transfer systems

- Supports up to 40-bit Deep-Color in RGB/YCbCCr/RGBW/RGB/Y format Digital Video Output with selectable edge clocking

-

V-by-One 1.4 Transmitter

- Compliant with V-by-One 1.4 specification

- Support for up to 8 channels, with up to 4 Gbps data rate per channel

- Supports up to 40-bit Deep-Color in RGB/YCbCCr/RGBW/RGB/Y format Digital Video Output with selectable edge clocking

- Supports scrambling and 8b/10b encoding