UFS 3.1 Controller IP

Filter

Compare

8

IP

from

3

vendors

(1

-

8)

-

UFS 3.1 host

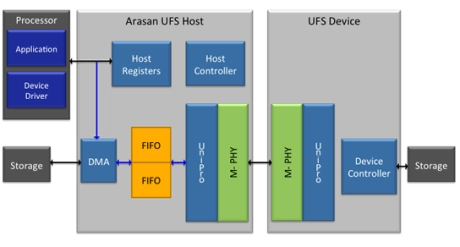

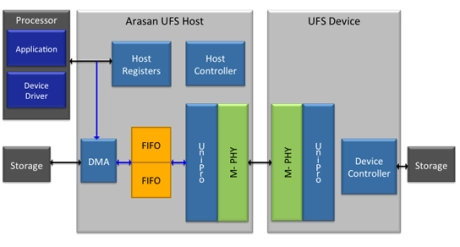

- The Universal Flash Storage 3.1 (UFS 3.1) is a simple but high-performance, serial interface primarily used in mobile systems, between host processing and nonvolatile eXecute-In-Place (XIP) or mass storage memory devices.

-

UFS Controller - Verifies compliance and performance of UFS interfaces in SoCs

- The UFS Controller Verification IP (VIP) ensures proper operation and compliance of UFS interfaces in SoC designs. It supports UFS 2.0, 2.1, 3.0, and 3.1 standards, enabling efficient validation of high-speed data transfers and power management.

- The VIP is critical for validating UFS controllers in a wide range of applications, from AI/ML systems to mobile devices and automotive infotainment. It ensures optimal performance, reliability, and seamless integration in diverse environments

-

UFS 2.1 Host Controller IP

- JEDEC UFS 2.0 and UFS HCI 2.0 Compliant

- Supports high performance M-PHY v3.0 type-1

- 2 lanes @ 5.9 Gbps per lane

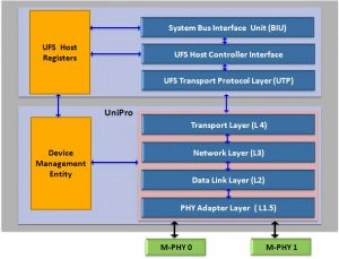

- UniPro v1.6 link layer

- Definable write-protect group size

-

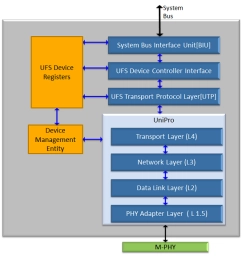

UFS 2.1 Device Controller IP

- The UFS 2.1 Device controller uses an M-PHY® 3.1 Adapter Layer backed by a UniPro v1.6 Link layer controller as per the specification.

- The UFS compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms.

-

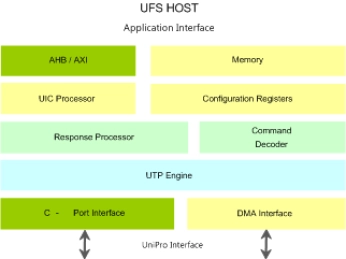

UFS HOST Controller IIP

- Supports high performance M-PHY type-1.

- Supports full UFS Host functionality.

- Supports UFS driver layer over UniPro.

- Supports configurable cport.

-

UFS 3.1 Device

- UFS 3.1 is the next specification update pending from JEDEC.

- Arasan will offer UFS 3.1 compatible Host and Device Controllers in late Q2 2017 to select customers.

-

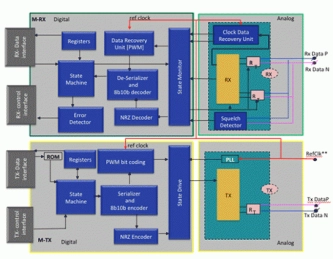

MIPI M-PHY® 3.1 Analog Transceiver

- The M-PHYs are of Type 1, which apply to UFS, LLI and CSI-3 protocols.

- The Multi-gear M-PHY 3.0 consists of analog transceivers, high speed PLL, data recovery units as well as the state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant to the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.

-

UFS 4.0 Host

- UFS 4.0 (JESD220F.pdf)

- UFS HCI 4.0 (JESD223E.pdf)

- MIPI UniPro version 2.0(mipi_UniPro_specification_v2-0.pdf)

- MIPI M-PHY version 5.0(mipi_M-PHY_specification_v5-0.pdf)