UCIe Chiplet Controller IP

Filter

Compare

9

IP

from

7

vendors

(1

-

9)

-

UCIe Chiplet PHY & Controller

- Compliant with the UCIe specification (2.0 & 1.1)

- Flexible Structure, easy to customize (Pre-hardened PHY tuned to Customer Spec, PHY + Adapter Layer, PHY + Adapter Layer + Customized Protocol Layer)

- Supports the CXS/AXI using the streaming package (AXI Interface bandwidth up to 89%)

-

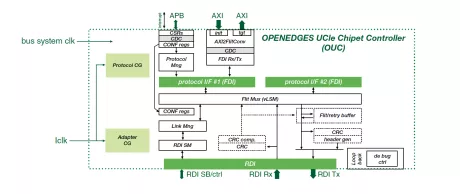

UCIe Die-to-Die Chiplet Controller

- High configurability and customizability

- Defines packets to communicate with a link partner using different AXI parameters

- Supports raw streaming modes

- Provides various Flit formats in UCIe v1.1 (filt format 2: 68B flit format, flit format 3/4: standard 256B flit format, and flit format 5/6: latency optimized 256B flit format)

-

UCIe PHY & Controller

- Lightweight die-to-die interconnect solution consisting of the Physical Layer, Die-to-Die Layer and Protocol Layer optimized for highest performance with the lowest power and area overhead that is compliant to the Universal Chiplet Interconnect Express (UCIe) 2.0 specification.

-

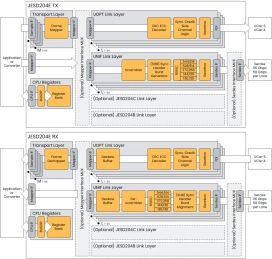

JESD204E Controller IP

- The JESD204E Controller IP from Chip Interfaces is an early adopter’s version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters.

- The JESD204-E IP core supports the UCIe Optimized Link Layer, a dedicated mode to run JESD over UCIe Modules with Line rates up the 64Gbps per bump, and a JESD204D backwards compatible mode called the Unified Link Layer with line speeds up to 116Gbps with PAM4 and 58Gbps with NRZ and full FEC support.

-

UCIe based 8-bit 48-Gsps Transceiver (ADC/DAC/PLL/UCIe)

- 48-Gsps peak sample rate

- 8 bit resolution

- UCIe SP (16x lanes at 16Gbps) with streaming controller

-

UCIe based 12-bit 12-Gsps Transceiver (ADC/DAC/PLL/UCIe)

- 12-Gsps peak sample rate

- 12 bit resolution (programmable)

- UCIe SP (16x lanes at 16Gbps) with streaming controller

-

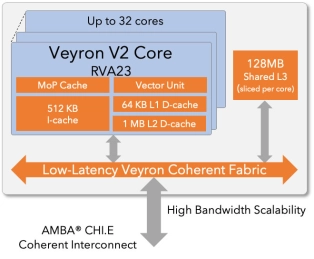

High-performance RISC-V CPU

- Fully compliant with the RVA23 RISC-V specification

- Comparable PPA to Arm Neoverse V3 / Cortex-X4

- Standard AMBA CHI.E coherent interface for SoC and chiplet integration

- Co-architected with Veyron E2 for seamless vector, AI acceleration, and big-little style heterogeneous compute configurations

-

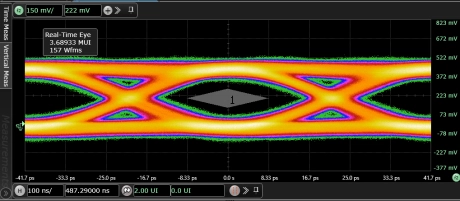

UCIe-S 64GT/s PHY IP

- The UCIe-S 64GT/s PHY IP is a cutting-edge solution designed to meet the growing demand for ultra-high-speed interconnects between dies in standard packaging environments.

- Leveraging the UCIe (Universal Chiplet Interconnect Express) 3.0 standard, this IP supports a blistering data rate of up to 64Gbps per lane, enabling next-generation AI, HPC, and data center SoC applications.

-

UCIe-A 64GT/s PHY IP

- The UCIe-A 64GT/s PHY IP is a cutting-edge solution designed to meet the growing demand for ultra-high-speed interconnects between dies in advanced packaging environments.

- Leveraging the UCIe (Universal Chiplet Interconnect Express) 3.0 standard, this IP supports a blistering data rate of up to 64Gbps per lane, enabling next-generation AI, HPC, and data center SoC applications.