SerDes IP

Filter

Compare

754

IP

from

70

vendors

(1

-

10)

-

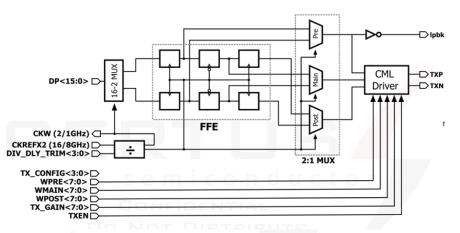

32Gbps SerDes PHY in GF 22nm

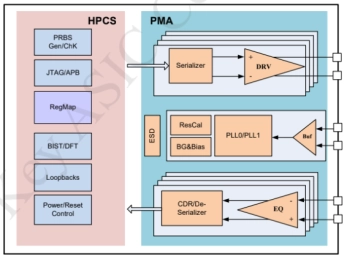

- This 32Gbps SerDes PHY is implemented in GlobalFoundries 22FDX CMOS technology and provides a high-performance, protocol-agnostic serial interface for advanced mixed-signal and high-speed digital SoCs.

- The PHY is architected as a modular design consisting of a low-jitter clock multiplier, a half-rate transmitter with digitally programmable feed-forward equalization, and a configurable CTLE-based receiver with digital clock-and-data recovery, supporting both 16 Gbps and 32 Gbps operation.

-

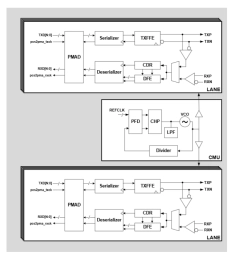

Ultra-Low Latency 32Gbps SerDes IP in TSMC 12nm FFC

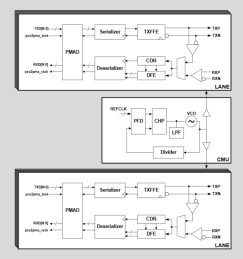

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Ultra-low latency 2/4/8-bit parallel interface mode for lowest possible latency

-

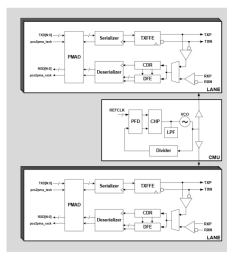

Ultra-Low Latency 32Gbps SerDes IP in TSMC 22nm ULP

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Ultra-low latency 2/4/8-bit parallel interface mode for lowest possible latency

-

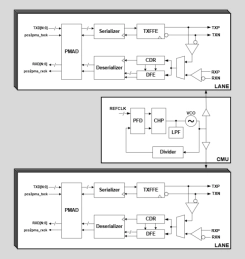

32Gbps SerDes IP in TSMC 12nm FFC

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Configurable low latency parallel data interface for optimal system performance

-

32Gbps SerDes IP in TSMC 22nm ULP

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Configurable low latency parallel data interface for optimal system performance

-

100G SerDes PAM4 PHY

- The SERDES PHY IP delivers a high-performance, low-power solution for high-speed interfaces up to 112Gbps.

- It supports diverse applications including AI accelerators, data centers, 5G infrastructure, and automotive SoCs.

-

SerDes

- High-speed SerDes with ultra-low-power consumption

- Industry’s fastest die to die communications

- Multiprotocol SerDes: HMC, PCIe, SATA, SAS, and USB and more

- High lane count with multiple data rates supported

-

SerDes Hard Macro-IP in GlobalFoundries 22FDX

- Low-power, flexible and robust Serializer-de-serializer IP built upon a proven ring-PLL based architecture,

- Support for multiple protocols, as well as custom-designed SerDes to meet specific needs and wide range data rates

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, 40, 64, or 80 bit

- Easy integration; delivered including all supplies, ESD and RDL for your bump pitch

-

-

1-56Gbps Serdes - 7nm (Multi-reference Clock)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.