Security Processor IP

Filter

Compare

154

IP

from

44

vendors

(1

-

10)

-

32-Bit Security processor

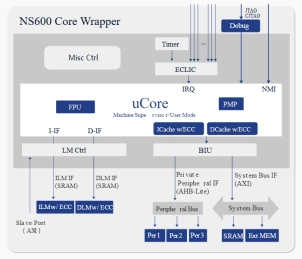

- Nuclei Security processor is a series of chips designed specifically for security application scenarios, including NS100, NS300, and NS600 products.

-

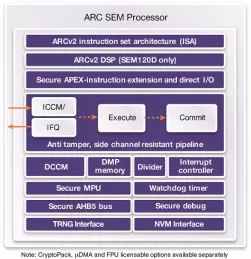

ARC SEM120D Security Processor with DSP for Low Power Embedded Applications

- Performance-, power- and area-efficient security processors for embedded applications

- Secure privilege mode orthogonal to kernel/user mode

- Enhanced secure MPU with context ID for secure or normal operation

- Up to 16 configurable protected regions and per region scrambling capability

-

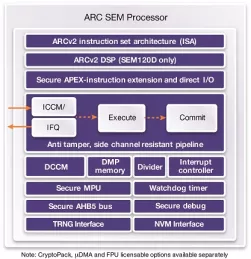

ARC SEM110 Security Processor for Low Power Embedded Applications

- Performance-, power- and area-efficient security processors for embedded applications

- Secure privilege mode orthogonal to kernel/user mode

- Enhanced secure MPU with context ID for secure or normal operation

- Up to 16 configurable protected regions and per region scrambling capability

-

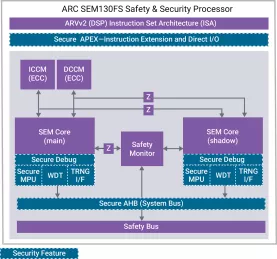

ARC SEM130FS Safety and Security Processor

- ASIL D compliant dual-core, lockstep safety processor supports ISO 26262 automotive safety standards and provides advanced security to protect against evolving threats

- Secure privilege mode orthogonal to kernel/user mode

- Integrated self-checking safety monitor capable of time diversity

- Uniform instruction timing and timing/ power randomization for side channel resistance

-

IEEE 802.1ae (MACsec) 100G Security Processor with Avalon-ST Interface

- Small size combined with high performance

- Self-contained

- Very low latency

-

IEEE 802.1ae (MACsec) Security Processor

- Small size combined with high performance:

- Self-contained, uses two external memories for key storage and statistic counters

- Very low latency

- Back-to-back packet processing

-

IPsec Security Processor

- Support for IPv4 and IPv6 packets

- Support for the IPsec ESP and AH protocols:

- Support for IPsec ESP encryption algorithms per RFC 4835:

- Support for IPsec ESP (and AH for –AH option) authentication algorithms per RFC 4835:

-

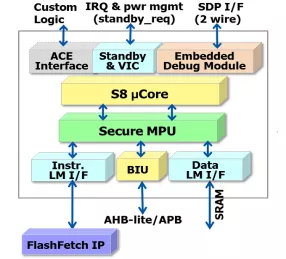

Compact Processor for Security

- Secure MPU against memory tampering

- Shields against side-channel attack

- Secure debug for multi-party software development

- Flexible configurations and run-time control

-

Performance-efficient, ultra-low power, compact ARC SEM security processors help protect against logical, hardware, physical and side-channel attacks

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

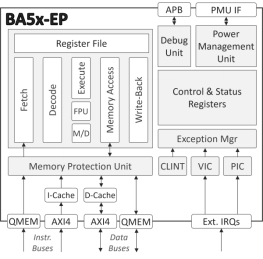

Enhanced-Processing Embedded RISC-V Processor

- The BA5x-EP is a highly-featured 32-bit RISC-V embedded processor IP core optimized for complex, processing-demanding applications.

- It is equipped with a floating-point unit and cache memories, supports hardware-level virtualization, and is suitable for concurrent execution in a multi-processor environment.