Samsung 8nm IP

Filter

Compare

24

IP

from

5

vendors

(1

-

10)

-

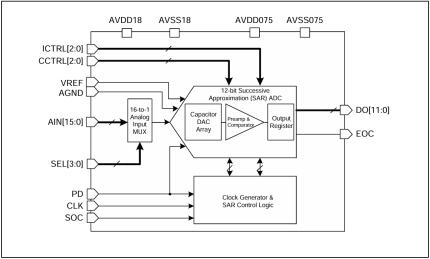

12-bit ADC on Samsung 8nm LN08LPP

- The sf_adc0802x_ln08lpp_306011 is a 1.8V/0.75V dual supply-voltage 16-ch 12-bit analog-to-digital converter (ADC) that supports conversion rate (FS) up to 1MS/s, designed in 8nm CMOS FinFET process.

- It consists of a 16-to-1 analog input MUX, a successive approximation (SAR) type monolithic ADC, a clock generator, and level-shifters for low voltage digital interface.

-

16b 80Msps DAC with 10KHz BW in samsung 8nm

- Technology: Samsung 8nm LPP process

- Metal Scheme:11M_3Mx_6Dx_1Gx_1Iz_LB

- Programmable Gain

- Programmable Offset

-

12b, 2Gsps, Self-Calibrating Current Steering IQDAC in samsung 8nm for 5G & WIFI6

- Technology: Samsung 8nm LPP process

- Metal Scheme: 11M_3Mx_6Dx_1Gx_1Iz_LB

- 12b Resolution, Fs = 2Gsps

- Programmable 20mA Differential Current source

-

Dual channel 12-bit, 2GS/s ADC for 5G & WIFI6 in Samsung 8nm

- Technology: Samsung 8nm LPP process

- Metal Scheme:11M_3Mx_6Dx_1Gx_1Iz_LB

- Dual channel 12-bit, 2GS/s Analog-to-Digital Converter

-

14b, 4Gsps, Self-Calibrating Current Steering IQ DAC for 5G & WIFI6 in samsung 8nm

- Samsung 8nm LPP process

- Metal Scheme: 1p8m_5x2z

- 14b Resolution, Fs = 4Gsps

-

12b, 1Gsps, Self-Calibrating Current Steering IQDAC in samsung 8nm for 5G & WIFI6

- • Technology: Samsung 8nm LPP process

- • Metal Scheme:

- 11M_3Mx_6Dx_1Gx_1Iz_LB

- • 12b Resolution, Fs = 1Gsps

-

Dual channel 12-bit, 1GS/s ADC in Samsung 8nm for 5G & WIFI6

- • Technology: Samsung 8nm LPP process

- • Metal Scheme:11M_3Mx_6Dx_1Gx_1Iz_LB

- • Dual channel 12-bit, 1GS/s Analog-to-Digital Converter

- • Differential analog input

-

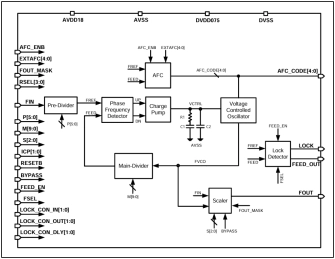

Integer PLL on Samsung 8nm LN08LPP

- PLLF0816X is a 1.8V/0.75V dual supply-voltage phase locked loop (PLL) with a wide-output-frequency-range for frequency synthesis.

- It consists of a phase frequency detector (PFD), a charge pump, a voltage-controlled oscillator (VCO), a 6-bit pre divider, a 10-bit main-divider, a 3-bit scaler, and an automatic frequency control (AFC).

-

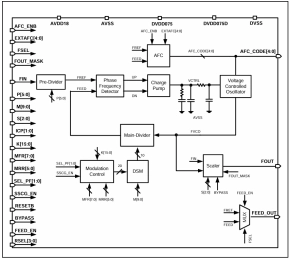

Frac-N PLL on Samsung 8nm LN08LPP

- PLLF0842X is a 1.8V/0.75V dual supply-voltage phase locked loop (PLL) with a wide-output-frequency-range for frequency synthesis.

- It consists of a phase frequency detector (PFD), a charge pump, a voltage-controlled oscillator (VCO), a 6-bit pre divider, a 10-bit main-divider, a 3-bit scaler, a delta-sigma modulator (DSM) and an automatic frequency control (AFC).

-

Temperature Sensor, +/-3C Accuracy without Trimming - Samsung 8nm

- Temperature Sensor, +/-3C Accuracy without Trimming;