Samsung IP

Filter

Compare

191

IP

from

28

vendors

(1

-

10)

-

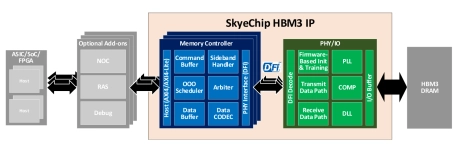

High Bandwidth Memory 3 (HBM3/3E) IP optimized for Samsung SF4X

- The HBM3 IP consists of a PHY and memory controller optimized for Samsung SF4X process to support the HBM3 memory standard (JESD238A) operating at up to 9.6 Gbps/pin.

- The HBM3 IP is designed for high memory throughput and low latency applications while minimizing area and power consumption.

-

USB3.0 PHY on GF22FDX and Samsung 28nm FDSOI

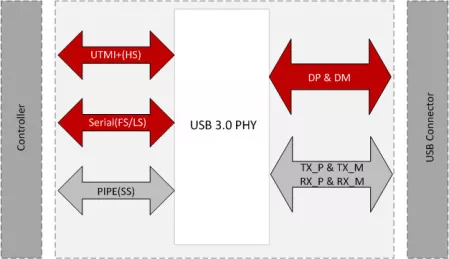

- The USB3.0 PHY IP is designed according to the USB 3.0, USB2.0 Specification.

- It supports the USB3.0 5Gbps Super-Speed mode and backward compatibles with the USB2.0 480Mbps High-Speed, 12Mbps Full-Speed, and 1.5Mbps Low-Speed modes

- The USB 3.0 PHY interface complies with PHY Interface for PCI Express and USB3.0 Architectures specification (PIPE 3.0) and the USB2.0 PHY interface complies with the UTMI v1.05 specification.

-

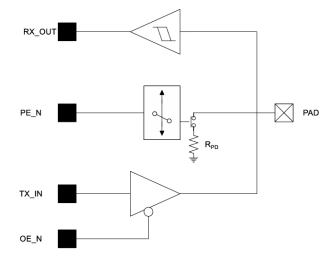

1.8V Capable GPIO on Samsung Foundry 4nm FinFET

- The 1.8V capable GPIO is an IP macro for on-chip integration. It is a 1.8V general purpose I/O built with a stack of 1.2V MOS FINFET devices. It is controlled by 0.75V (core) signals.

- Supported features include core isolation, output enable and pull enable. Extra features such as input enable/disable, programmable drive strength and pull select, can be supported upon request.

-

16b 80Msps DAC with 10KHz BW in samsung 8nm

- Technology: Samsung 8nm LPP process

- Metal Scheme:11M_3Mx_6Dx_1Gx_1Iz_LB

- Programmable Gain

- Programmable Offset

-

12b, 2Gsps, Self-Calibrating Current Steering IQDAC in samsung 8nm for 5G & WIFI6

- Technology: Samsung 8nm LPP process

- Metal Scheme: 11M_3Mx_6Dx_1Gx_1Iz_LB

- 12b Resolution, Fs = 2Gsps

- Programmable 20mA Differential Current source

-

Dual channel 12-bit, 2GS/s ADC for 5G & WIFI6 in Samsung 8nm

- Technology: Samsung 8nm LPP process

- Metal Scheme:11M_3Mx_6Dx_1Gx_1Iz_LB

- Dual channel 12-bit, 2GS/s Analog-to-Digital Converter

-

12-bit, 6MS/s ADC for Microcontroller Business in Samsung LFR6LP

- Process Node: Samsung LFR6LP

- 12-bit SAR ADC @ 6MS/s conversion range.

- The ADC power scales linearly with clock speed. (DC to 6Msps)

- Single-ended/ Differential input modes

-

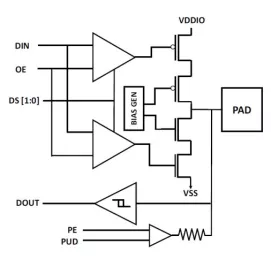

1.8V/3.3V Switchable GPIO with 5V I2C Open Drain and Analog Cells in Samsung 11nm

- A Samsung 11nm Flip-Chip I/O library with dynamically switchable 1.8V/3.3V GPIO with fail-safe capability, 5V I2C / SMBus open-drain cell, 5V OTP cell, 1.8V 3.3V analog cells, and associated ESD.

- A key attribute of this library is its ability to detect and dynamically adjust to a VDDIO supply of 1.8V or 3.3V during system operation.

- The GPIO cell can be configured as input, output, open source, or open drain with an optional internal 50K ohm pull up or pull down resistor.

-

Ultra-low quiescent capacitor-less LDO voltage regulator in Samsung Foundries 65nm LFR6LP

- Ultra-low quiescent current to enable very low power consumption in sleep and deep sleep mode

- Low BoM, no external capacitor required

- Embedded voltage reference

-

Low-power Power-On-reset design in Samsung Foundries 65nm LFR6LP process

- Low-power power-on-reset solution for power-critical IoT applications (50 nA operating current)