SRAM IP

Filter

Compare

731

IP

from

82

vendors

(1

-

10)

-

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage, 6T(L110) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

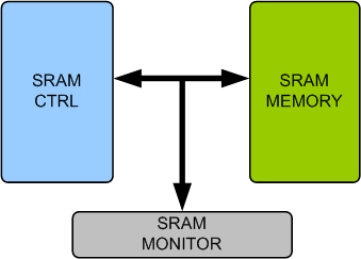

SRAM Test Solution

- EZ-TEC can coexist with the existing memory testing circuits of chip design companies.

- This U. S. patent breaks down memory testing algorithms into elements, allowing users to reconstruct the architecture of any memory testing algorithm through element reorganization.

-

SRAM Test and Repair Solution

- EZ-Safety is a dedicated IP designed for automotive electronic chips.

- It can meet the ISO 26262 specifications and assist automotive chip design companies in developing chips that comply with ISO 26262 standards more efficiently.

-

SRAM Test and Repair Solution

- EZ-Monitor ensures the memory lifecycle within the chip, and effectively monitor the lifecycle of each individual chiplet.

-

QDR II SRAM Controller Intel® FPGA IP Function

- The QDR II SRAM Controller Intel FPGA IP provides an easy-to-use interface to QDR II SRAM and QDR II+ SRAM modules

- The QDR II SRAM controller ensures that the placement and timing are in line with QDR II specifications

- The QDR II SRAM controller’s local interface is compatible with the Intel FPGA Avalon® Memory-Mapped interface, for easy integration into Intel Qsys IP.

-

QDR II SRAM Controller Intel® FPGA IP

- The QDR II SRAM Controller Intel® FPGA IP function provides an easy-to-use interface to QDR II SRAM modules

- The QDR II SRAM Controller ensures that the placement and timing are in line with QDRII specifications.

-

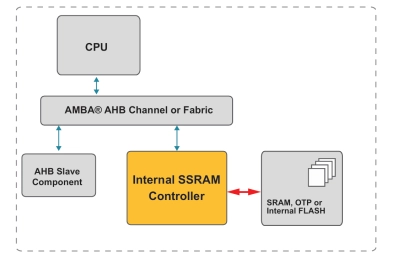

AHB SRAM Controller

- The AHB SRAM Controller provides a standard AHB interface to translate AHB bus reads and writes into reads and writes with the signaling and timing of a standard 32-bit synchronous SRAM.

- The AHB SRAM Controller provides zero-wait-state AHB access to the synchronous SRAM in all cases except for the following back-toback events: an AHB write directly followed by an AHB read.

-

-

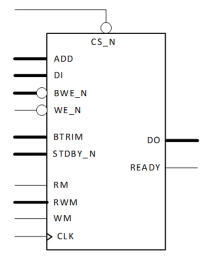

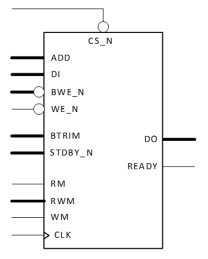

SRAM Memory Model

- Supports SRAM memory devices from all leading vendors.

- Supports 100% of SRAM protocol standard.

- Supports all the SRAM commands as per the specs.

- Supports Automated power down when deselected.