RapidIO Controller IP

Filter

Compare

6

IP

from

4

vendors

(1

-

6)

-

RapidIO Controller with V4.1 Support

- The RapidlO Controller solution (GRIO™) is a highly flexible and configurable IP.

- The RapidlO Controller Solution can be used as a Host or device.

- The RapidlO Controller when used along with the RapidlO to AXI Bridge (RAB) provides high speed multi-channel DMA Data Message and Data streaming functionality to match the bandwidth requirements of the RapidlO interface.

-

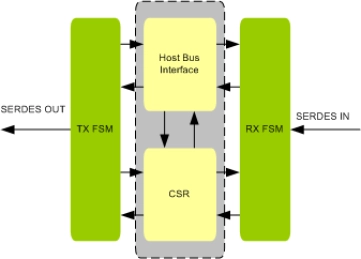

Serial RapidIO Controller

- Fully compliant with the RapidIO specification revision 2.2,

- Simple transaction interface with Host processor and DMA Engine,

- Configurable FIFOs implemented by BlockRAM in both transmit and receive paths,

- Register file containing all necessary architectural registers providing total software control of IP core,

-

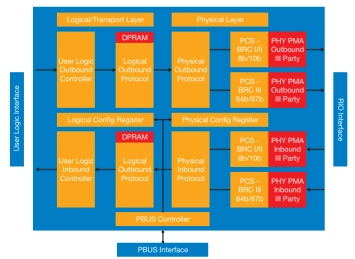

RAPIDIO EndPoint Controller IIP

- Compliant with RapidIO Interconnect 2.2 specification

- Supports all Capability Registers(CARs) and Configuration and Status Registers(CSRs)

- Supports high link utilization and low latency

- Supports efficient receive and transmit buffering scheme

-

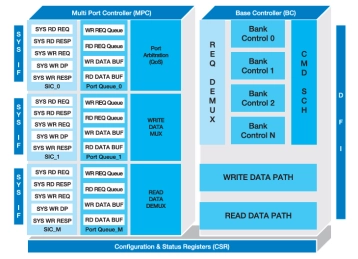

Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC Controller is a highly flexible and configurable design. It is targeted for high bandwidth access and low power consumption such as next generation mobile, DDR/LPDDR networking and consumer applications.

- The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities.

-

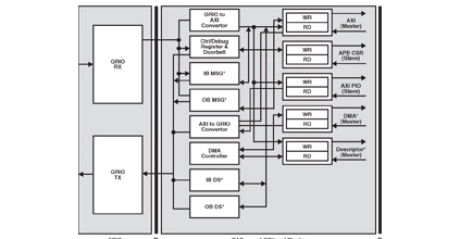

RapidIO to AXI Bridge (RAB)

- The RapidlO-AXI Bridge (RIO-AXI Bridge) is a highly flexible and configurable IP used along with the native RapidlO Controller (GRIO) to provide RapidlO interface on one side and AXI interface on the system side.

- The Bridge has been architectured to interface with a RapidlO controller used as a Host or device.

- The RIO-AXI BRIDGE uses high speed multi-channel DMA Messaging and data streaming controllers to match the bandwidth requirements of the RIO solution.

-

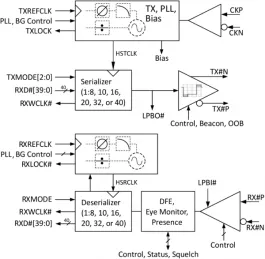

Multiprotocol SerDes PMA

- Supports over 30 protocols including CEI 6G & 11G SR, MR, LR, Ethernet 10GBASE-X/S/K/R, PCIe Gen1/2/3/4, V-by-One HS/US, CPRI, PON, OTN/OTU, 3GSDI, JESD204A/B/C, SATA1-3, XAUI, SGMII

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, or 40 bit

- Tx ring PLL includes fractional multiplication, spread spectrum and Jitter Cleaner function for Sync-E and OTU

- Core-voltage line driver with programmable pre-and post-emphasis