RRAM IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

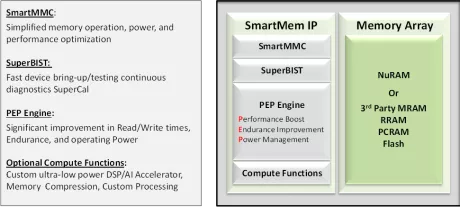

SmartMem Subsystem IP

- Fully synthesizable and configurable memory subsystem IP that enables significant improvement in power, performance and endurance not only for NuRAM but also other third party MRAMs as well as RRAM, PCRAM and Flash