PLL in TSMC 28nm IP

Filter

Compare

128

IP

from

8

vendors

(1

-

10)

-

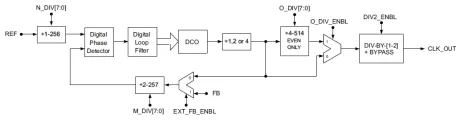

Ultra-Low Power Fractional PLL IP in in TSMC (12/16nm FFC, 22nm ULP/ULL, 28nm HPC+)

- Supports wide input frequency range: 10MHz to 240MHz

- Supports 3:1 output frequency range allows optimization for power and jitter performance

- 24-bit fractional accuracy

- Supports Spread Spectrum Clocking

-

LPDDR4 multiPHY V2 in TSMC (28nm, 22nm, 16nm, 12nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

-

USB 2.0 picoPHY in TSMC (40nm, 28nm)

- Complete mixed-signal physical layer for single-chip USB 2.0 OTG and non-OTG applications

- Small PHY macro area

- Low power

- Advanced power management features, including support for power supply gating, supply scaling, ultra-low standby current support, and power management unit (PMU) interrupt support

-

USB 2.0 femtoPHY in TSMC (40nm, 28nm, 22nm, 16nm, 12nm, 10nm, N7, N6, N5, N3P)

- Complete mixed-signal physical layer for single-chip USB 2.0 Host, Device, and Dual Role applications Small PHY macro area: as small as 0.20 mm2

- Low power: as low as 50mW (during high-speed packet transmission)

- Advanced power management features including support for power supply gating, supply scaling, ultra-low standby current support, and power management unit (PMU) interrupt support

- Supports USB 2.0 ID-pin detection and OTG Voltage Detectors

-

TSMC CLN28HPCLVT 28nm Deskew PLL - 220MHz-1100MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN28HPCLVT 28nm Deskew PLL - 440MHz-2200MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN28HPCLVT 28nm Deskew PLL - 880MHz-4400MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN28HPC+LVT 28nm Deskew PLL - 225MHz-1125MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN28HPC+LVT 28nm Deskew PLL - 450MHz-2250MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.