PCIe 6.1 IP

Filter

Compare

6

IP

from

3

vendors

(1

-

6)

-

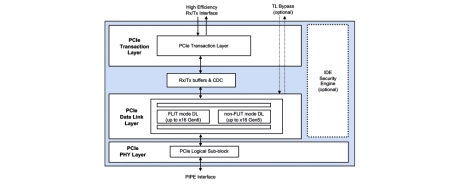

PCIe 6.1 Controller with AXI

- The PCI Express® (PCIe®) 6.1 Controller with AXI is configurable and scalable controller IP designed for ASIC implementation.

- The controller supports the PCIe 6.1 specification, including 64 GT/s data rates, PAM4 signaling, FLIT mode, and L0p power state.

-

PCIe 6.1 Controller

- Designed to the latest PCI Express 6.1 (64 GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1/3.0 (8 GT/s), and PIPE 6.x (8, 16, 32, 64 and 128-bit) specifications

- Supports SerDes Architecture PIPE 10b/20b/40b/80b width

- Supports original PIPE 8b/16b/32b/64b/128b width

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports multiple virtual channels (VCs) in FLIT and non-FLIT modes

- Supports Endpoint, Root-Port, Dual-mode, Switch port configurations

-

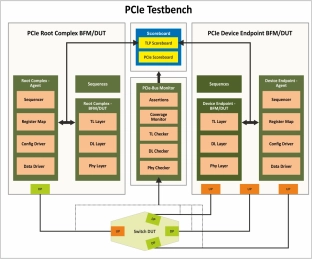

PCIe Switch Verification IP

- Compliant with the PCIe 6,5,4,3 specification.

- Support Pipe Specification 6.1.1

- NVMe on top of Low Power, CXS, CPI, CXL, CXL Security, PCIe Gen6/5/4/3 management

- Supports Pipe Specification 6.1 with both Low Pin Count and Serdes Architecture.

-

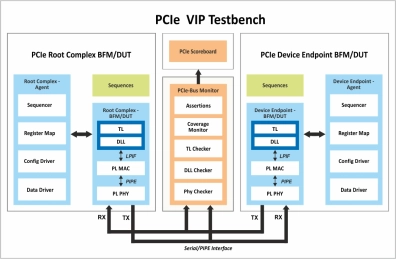

PCIe Gen 6 Verification IP

- Compliant with PCI Express Specifications 6.1 (64GT/s), 5.0 (32GT/s), 4.0 (16GT/s), 3.1 (8GT/s), 2.0 (5GT/s) and 1.1 (2.5GT/s).

- Support for 64.0 GT/s Data Rate per lane with backwards compatible.

- Support for new PAM4 Signalling and Gray Coding.

- Support for both Flit Mode & Non-Flit Mode.

-

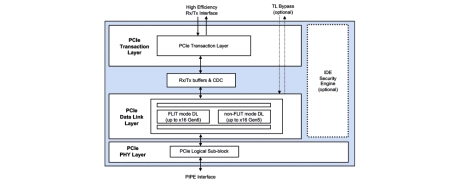

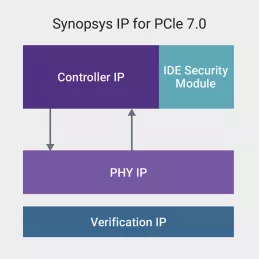

PCIe 6.0 Integrity and Data Encryption Security Module

- Compliant with PCI Express IDE specification

- Support for TDISP

- High-performance AES-GCM based packet encryption, decryption, authentication

- Seamless integration with Synopsys controllers via TLP packet-based interface

- FLIT mode support

-

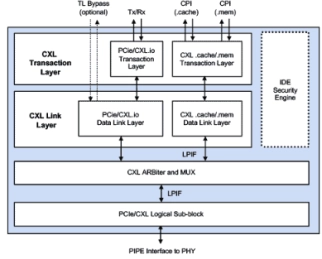

CXL 3.1 Controller

- Ultra-low Transmit and Receive latency

- Internal data path size automatically scales up or down (256, 512 or 1024 bits) based on max. link speed and width for optimal throughput

- Supports backwards compatibility to PCIe 6.1

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Optional QuickBoot mode allows for up to 4x faster link training, cutting system-level simulation time by 20%

- Loopback Mode support at DLL for CXL.mem and CXL.cache protocols

- Merged Replay and Transmit buffer enables lower memory footprint