NVME IP

Filter

Compare

97

IP

from

21

vendors

(1

-

10)

-

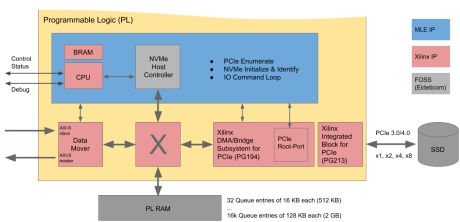

NVMe Streamer

- Provides one or more NVMe / PCIe host ports for NVMe SSD connectivity

- Full Acceleration means “CPU-less” operation

- Fully integrated and tested NVMe Host Controller IP Core

- PCIe Enumeration, NVMe Initialization & Identify, Queue Management

-

ARTIX Ultra Scale Plus NVME HOST IP – Gen4

- When using a PCIe RP IP configured in Gen4 the system frequency is at 250MHz/256-Bits.

- When using a PCIe RP IP configured in Gen3 the system frequency is at 125MHz/256-Bits.

-

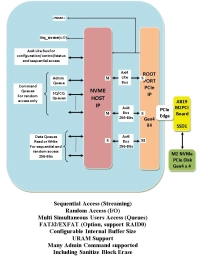

Kintex Ultra Scale Plus NVMe Host IP

- The LDS NVME HOST IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

- The register file interface simplify the management of the IP for CPU interface or State Machine interface using AXI bus.

-

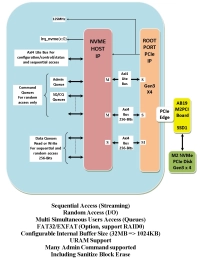

AGILEX 7 R-Tile Gen5 NVMe Host IP

- The LDS NVME HOST IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

- The register file interface simplify the management of the IP for CPU interface or State Machine interface using Avalon bus.

-

NVMe Controller

- Compliant to NVM Express 1.4 specification

- Support for configurable number of IO Queues

- Support for configurable Queue depth

- Support for Round Robin or Weighted Round Robin with Urgent Priority arbitration mechanism

-

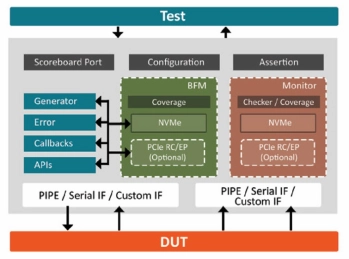

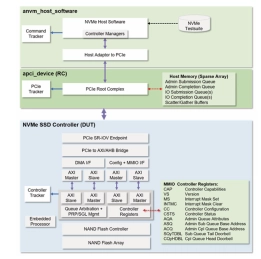

NVMe Verification IP

- The NVMe Verification IP (VIP) and Post-Silicon Validation Suite are based on the latest protocol standards (NVMe 1.2) from www.nvme.org. These are available from elnfochips for licensing with support and related services.

-

NVMe 2.2 Verification IP

- Compliant with the NVMe 2.2, 2, 1.4, 1.3, 1.2 specification.

- Compliant with PCI Express Specifications 6.3 (64GT/s), 5.0 v1.0(32GT/s), 4.0 v1.0 (16GT/s), 3.0 (8GT/s), 2.0 (5GT/s) and 1.1 (2.5GT/s).

- Compliant with PIPE Specification 6.2, 5.1, 4.4.1.

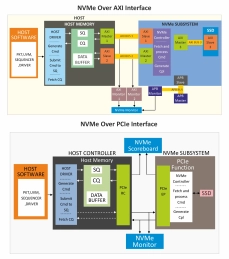

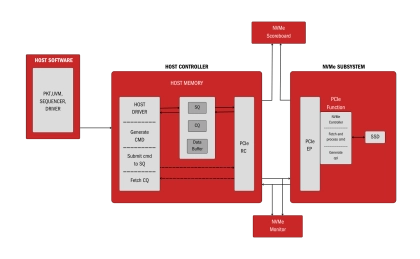

- NVMe on top of Low Power, AXI, PCIe Gen6/5/4/3 management

-

Verification IP for NVMe

- Accelerated confidence in simulation-based verification of RTL designs with NVMe interfaces over PCIe or Fabric links

-

NVMe Gen 5 Controller - Ensures efficient, high-speed data transfer and error-free operation in storage systems

- The NVMe Gen 5 Controller Verification IP ensures that storage systems operate efficiently at 32 GT/s data transfer rates. It supports compliance with NVMe 1.4/1.5 specifications by automating protocol checks, error injection, and debugging tools.

- This tool is crucial for validating SSDs and memory modules, improving system stability and ensuring compatibility in enterprise-grade applications. It also accelerates time-to-market by ensuring storage systems meet industry standards.

-

NVMe Gen5 Controller - Enhances data transfer speeds and reduces latency for storage systems

- The NVMe Gen 5 Controller is engineered to harness the power of PCIe Gen 5, delivering up to 32 GT/s per lane for significantly faster data transfers, improved throughput, and reduced latency. This controller enhances SSD performance for demanding applications.

- With support for advanced error correction, low power consumption, and superior scalability, the NVMe Gen 5 Controller is ideal for high-performance computing, AI, data centers, and next-gen storage solutions, meeting the needs of modern, data-intensive workloads.