MIPI I3C HCI controller IP

Filter

Compare

6

IP

from

2

vendors

(1

-

6)

-

MIPI I3C Total IP Solution

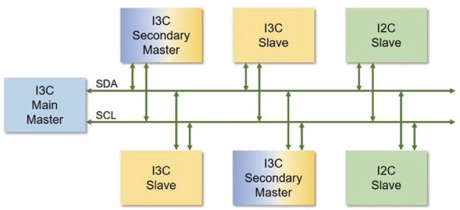

- The MIPI I3CⓇ Total IP solution is a seamless integration of MIPI I3CⓇ controller, MIPI I3CⓇ PHY I/O, and MIPI I3CⓇ software stack.

- The MIPI I3CⓇ Total IP solution is a simplified, backward compatible with I2C, scalable, and cost-effective interface.

-

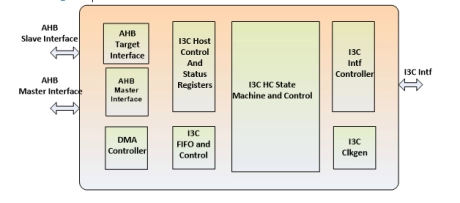

I3C Host Controller IP v1.2

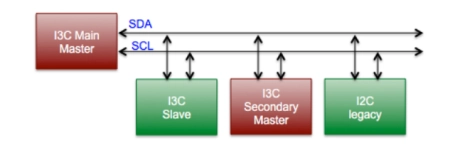

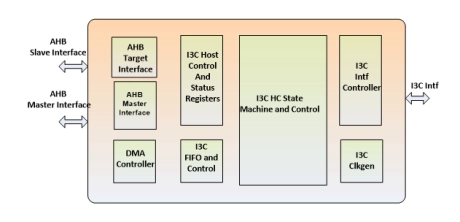

- The I3C Host Controller IP implements Host Controller functionality as defined by the MIPI Alliance’s I3C Specification.

- The I3C bus is used for various sensors in the mobile/automotive system where the Host Controller transfers data and control between itself and various sensor devices.

- The I3C Host Controller IP Core provides a 32-bit AHB bus as the application interface to configure and control the I3C Host Controller IP Core.

-

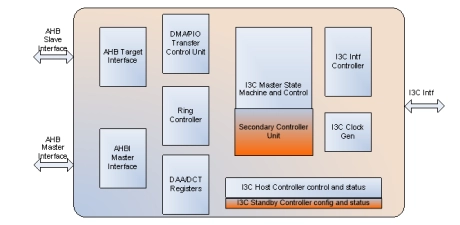

I3C Dual/Secondary Controller IP v1.2

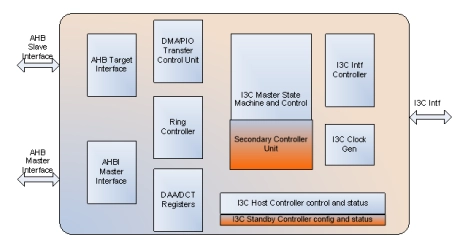

- The I3C Secondary Controller IP Core implements Active controller functionality as defined by the MIPI Alliance’s I3C Specification and Secondary Controller logic.

- The I3C bus is used for various sensors in the mobile/automotive system where the active controller transfers data and control between itself and various sensor devices.

-

I3C Dual/Secondary Controller IP

- Overview

- The Arasan I3C Secondary Controller IP Core implements Active controller functionality as defined by the MIPI Alliance’s I3C Specification and Secondary Controller logic. The I3C bus is used for various sensors in the mobile/automotive system where the active controller transfers data and control between itself and various sensor devices. In some applications, the active controllers can handoff the controller role to the secondary controller on the bus. The Dual role IP joins the I3C bus as a secondary controller (as a target) and will request/accept the controller role. The IP core provides a 32bit AHB bus as application interface to configure and control the transfers. The controller manages the control signal to IO buffers during the active and standby mode. Please note that the User needs to provide appropriate IO buffers to meet the I3C specification.

- The I3C Dual Controller implements support for legacy I2C Slave devices, Clock frequency scaling, Open-drain and Push-pull operation of I3C Interface, and Dynamic Addressing support. The I3C Dual Controller supports the required SDR mode with Clock frequency of up to 12.5 MHz and also the HDR mode (HDR-DDR) as defined by the I3C Specification.

-

I3C 1.1 Host Controller

- The I3C Host Controller IP implements Host Controller functionality as defined by the MIPI Alliance’s I3C Specification.

- The I3C bus is used for various sensors in the mobile/automotive system where the Host Controller transfers data and control between itself and various sensor devices.

- The I3C Host Controller implements support for legacy I2C Device Controllers, Clock frequency scaling, Open-drain and Push-pull operation of I3C Interface, and Dynamic Addressing support.

-

Verification IP for I3C/I2C

- A comprehensive memory VIP solution portfolio for I3C and I2C s used by system-on-chip (SoC) and IP designers to ensure comprehensive verification and protocol and timing compliance.

- Avery Verification IP for Control/Serial Buses implements a complete set of models, protocol checkers and compliance testsuite in 100% native SystemVerilog and UVM.