MIPI DSI IP

Filter

Compare

379

IP

from

27

vendors

(1

-

10)

-

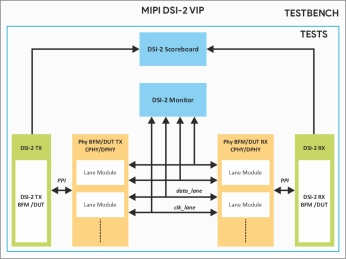

MIPI DSI v2.2 Verification IP

- Compliant to MIPI DSI Specification version 2.2 and MIPI C-PHY Specification version 2.1 with PPI interface.

- Support all Calibration Format & operations

- C-PHY supports MFAA and SFAA for DSI TX and RX respectively for Data Lane Module in command mode.

- C-PHY supports MFAN and SFAN for DSI TX and RX respectively for data Lane Module in video mode.

-

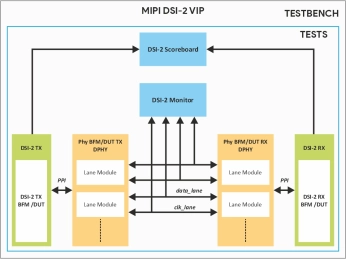

MIPI DSI v1.3.2 Verification IP

- Compliant to MIPI DSI Specification version 1.3.2 and MIPI D-PHY Specification version 1.2 with PPI interface.

- Support all Calibration Formats & operations

- D-PHY supports MFAA and SFAA for DSI TX and RX respectively for Data Lane Module in command mode.

- D-PHY supports MFAN and SFAN for DSI TX and RX respectively for Data Lane Module in video mode.

-

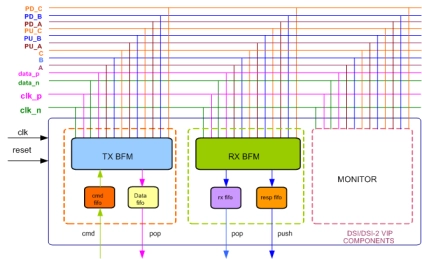

MIPI DSI Verification IP

- Full MIPI DSI Transmitter and Receiver functionality.

- Supports 1.3.1 MIPI DSI/2.0 MIPI DSI-2 Specifications.

- Supports PPI interface.

- Operates as a Transmitter, Receiver, or both.

-

MIPI DSI Synthesizable Transactor

- Full MIPI DSI Transmitter and Receiver functionality.

- Supports MIPI DSI v1.3 and MIPI DSI-2 v1.1 Specifications.

- Supports PPI interface.

- Operates as a Transmitter, Receiver, or both.

-

MIPI DSI Host Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI Host Combo Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI Transmitter v1.2 Controller IP, Compatible with MIPI D-PHY & C-PHY

- MIPI Alliance Specification for Display Serial

- MIPI display type 1, type 2, type 3 and type 4

- Video mode (Non-Burst with Sync Pulses, Non-Burst with Sync Events and same for Burst mode).

- TE feature (Tearing Effect) for command display

-

RGB to MIPI DSI Display Interface Bridge

- Supports MIPI DSI and MIPI CSI-2 outputs up to 6 Gbp: 1, 2 or 4 data lanes

- Supports parallel MIPI DPI, CMOS, RAW and RGB interfaces at up to 300 MHz

- Supports CSI-2 compatible video formats (RAW, RGB, and YUV):

- Supports DSI compatible video formats (RGB):

-

OpenLDI LVDS to MIPI DSI Display Interface Bridge

- Supports MIPI DSI Input at up to 12 Gbps

- Supports OpenLDI LVDS at up to 9.6 Gbps

- Supports single or dual link LVDS to single or dual MIPI DSI outputs

- Supports DSI compatible video formats (RGB) :

-

One Input to Two Output MIPI DSI Display Splitter Bridge

- Supports MIPI DSI up to 6 Gbps per MIPI D-PHY

- Provides one or two MIPI DSI outputs

- Supports all MIPI DSI data types

- Provides a DCS (Display Command Set) controller to program the display, ROM data used only for DSI in HS or LPDT mode – ROM is programmable by user