MIPI CSI Controller IP

Filter

Compare

14

IP

from

7

vendors

(1

-

10)

-

MIPI CSI Controller Subsystems

- Support for 1 to 4 PPI Lanes

- Line rates ranging from 80 to 1500 Mb/s depending on the device family

- Multiple data type support (RAW,RGG,YUV)

- AXI IIC support for CCI interface

-

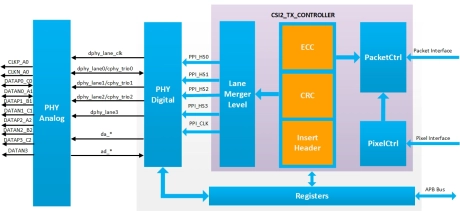

MIPI CD PHY Combo TX & RX + DSI & CSI Controller

- Our MIPI CD-PHY Transmitter and receiver PHY with Display Serial Interface (DSI) and Camera Serial Interface (CSI) Controllers are tailored for high-performance display and camera interface applications.

- These two PHY (TX and RX) integrated systems ensure seamless communication between the processor and display, the processor and camera; supporting high data rates and efficient power consumption.

-

MIPI D-PHY TX & RX + DSI & CSI Controllers

- Compliant with MIPI Committee Specifications

- High Data Rates: Supports data transmission rates up to 4.5Gbps per lane, allowing for high-resolution displays and smooth refresh rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Display Solution: Combines the MIPI D-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

-

MIPI D-PHY1.2 CSI/DSI TX and RX

- The MIPI D-PHY + DSI/CSI Controller IP is a versatile solution designed for high-speed data transmission in mobile and multimedia applications

- It supports MIPI D-PHY 2.0 standards

- The IP features a compact design with built-in I/O and ESD protection, optimized for robust performance and low power consumption

- It enables seamless connectivity with D-PHY based sensors, making it ideal for SoCs in consumer electronics, automotive, and IoT devices

-

MIPI C/D-PHY CSI/DSI TX and RX

- The MIPI C/D-PHY + DSI/CSI Controller IP is a versatile solution designed for high-speed data transmission in mobile and multimedia applications

- It integrates C-PHY and D-PHY in a single IP core, supporting both MIPI C-PHY 1.1 and D-PHY 2.0 standards

- The IP features a compact design with built-in I/O and ESD protection, optimized for robust performance and low power consumption

-

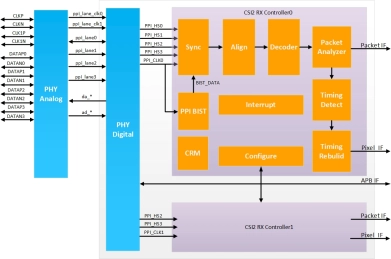

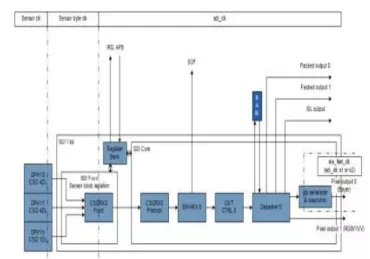

MIPI CSI-2 RX Controller Subsystem

- Support for 1 to 4 PPI Lanes

- Line rates ranging from 80 to 1500 Mb/s

- Multiple data type support (RAW,RGG,YUV)

- AXI IIC support for CCI interface

-

MIPI CSI-2 Receiver v1.3 Controller IP, Compatible with MIPI C-PHY & D-PHY

- MIPI Alliance Specification for Camera Serial

- Configurable DPHY Interface number

- Configurable Data Lane number (independent for each DPHY I/F)

- Configurable number of each output type

-

MIPI CSI-2 Receiver v1.1 Controller IP, Compatible with MIPI C-PHY & D-PHY

- MIPI Alliance Specification for Camera Serial

- Configurable DPHY Interface number

- Configurable Data Lane number (independent for each DPHY I/F)

- Configurable number of each output type

-

MIPI CSI-2 Receiver v2.0 Controller IP, Compatible with MIPI C-PHY & D-PHY

- MIPI Alliance Specification for Camera Serial

- Configurable DPHY Interface number

- Configurable Data Lane number (independent for each DPHY I/F)

- Configurable number of each output type