LDPC decoder IP

Filter

Compare

99

IP

from

21

vendors

(1

-

10)

-

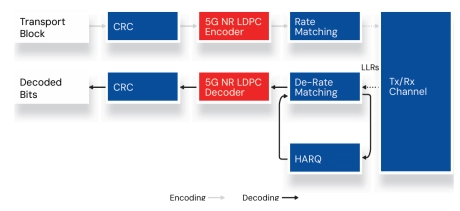

5G LDPC Decoder

- Low power design for HW implementation

- Minimum HW cost in ASIC implementation for LDPC decoder

- Optimized TDEC early termination algorithms to minimize power consumption

- Flexible HW architecture

-

NavIC LDPC Decoder

- Throughput matching the required specifications.

- Bit-Error-Rate (BER) and Block-Error-Rate (BLER) performance meet the required specifications.

- Compliant with 'ISRO-NAVIC-ICD-SPS-L1-1.0' standard

-

Flash Memory LDPC Decoder IP Core

- Quasi cyclic (QC) – Algebraic constructed – LDPC Code

- Regular Parity Check Matrix

- Codeword length: 16 K

- Code rate 0.953

- No or very low error floor

- Parallel/Layered decoding

-

LDPC Decoder for 5G NR and Wireless

- The 5G NR LDPC Decoder IP Core offers a robust solution for LDPC decoding, featuring a dedicated LDPC decoder block for optimal performance.

- It employs the Min-Sum LDPC decoding algorithm to ensure efficient decoding.

- The core allows for programmable internal bit widths at compile time, though the default values are usually sufficient.

-

(2048,1723) LDPC decoder for IEEE 802.3an 10GBASE-T

- Strong error correction performance

- Optimized method significantly lower the error floor at minimal cost

- High throughput with low complexity hardware

- Early termination technique

-

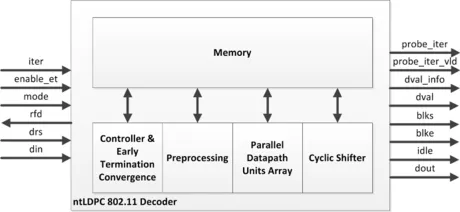

IEEE 802.11 n/ac/ax LDPC Decoder

- LDPC Decoder, support all IEEE 802.11 n/ac/ax defined block lengths (648, 1296, 1944) and code rates (1/2, 2/3, 3/4 and 5/6).

-

CCSDS Rate 1/2 TC and TM LDPC Decoder

- CCSDS TC and TM compatible

- Rate 1/2

- Data lengths of TC 64 and 256 or optional TM 1024 bits

- Includes ping-pong input and output memories

-

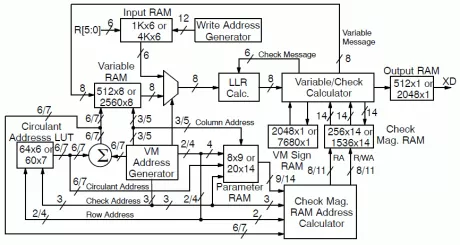

IEEE802.11n/ac/ax Wi-Fi LDPC Decoder and Encoder

- Layered decoding

- Soft decision decoding

- IEEE 802.11n/ac/ax standard compliant

- Support all LDPC code rates (½, 2/3 , ¾, and 5/6 )

- Support all LDPC codeword sizes(648, 1296, and 1944 bits)

-

Nonbinary LDPC Decoder

- Regular parity check matrix

- Soft decision SPA decoding

- Supports different code sizes

- Hard decision output

-

DVB-C2 LDPC Decoder IP

- Irregular parity check matrix

- Layered Decoding

- Minimum sum algorithm

- Configurable number of iterations