LDO IP

Filter

Compare

325

IP

from

47

vendors

(1

-

10)

-

10mA 3.3V Low-Dropout (LDO) Regulator on XFAB XT018

- The TS_VR_3V3_X8 is a 3.3V low-dropout linear regulator (LDO) to supply the digital core of an analog ASIC.

- The LDO operates with an input voltage of 5V (supply voltage) and provides an output regulated voltage of 3.3V.

- The LDO can supply a maximum DC load current of 10mA.

-

Low input voltage high performance LDO regulator in TSMC 22ULL

- LDO-T22-1-1.8-0.6-1.05_TSMC_22_ULL is a Low input voltage, high performance LDO linear regulator in TSMC 22ULL with programmable output voltage to supply core logic domains, SRAM arrays or RF/analog domains.

- It features normal and low-power (LP) operating modes to adjust the amount of output current depending on the application requirements.

-

Low Dropout (LDO) Capless Regulator - 300 mA Output on 7nm

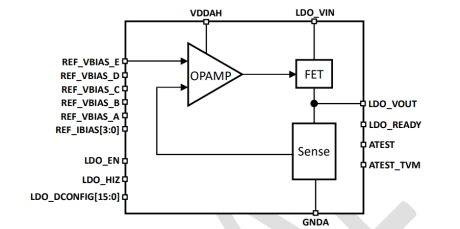

- The ODT-LDO-IC-300M-7 is a low dropout (LDO), linear regulator for integration in a SoC.

- The LDO uses advanced control techniques to achieve excellent transient response, excellent PSRR performance and low noise.

- The LDO has an integrated pass transistor and is stable with an on-chip capacitor of up to 1000pF.

-

Low Dropout (LDO) Regulator on TSMC 28nm

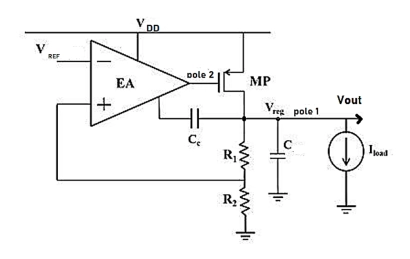

- The ODT-LDO-28HPCT is a low dropout (LDO), linear regulator for integration in a SoC.

- The LDO uses advanced control techniques to achieve excellent transient response, excellent PSRR performance and low noise.

- The LDO is stable with an off-chip capacitor of 1uF.

-

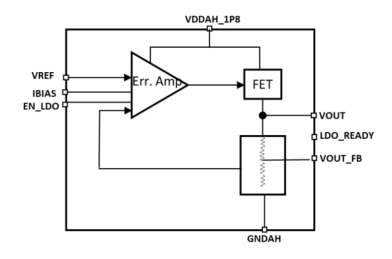

LDO regulator on SMIC 40nm, up to 12mA

- The present IP is a low-dropout (LDO) voltage regulator supporting a 12mA load current with an input voltage range of 2.7V to 3.6V (typical: 3.3V)

- It features three selectable output voltages: 0.9V, 1.1V, and 1.3V

- The reference voltage and bias current, derived from an integrated bandgap reference (BGR), are 0.6V and 0.5μA, respectively.

-

Capless LDO regulator on SMIC 65nm

- The present IP is a low-dropout (LDO) and capacitor-less voltage regulator developed using SMIC's 65nm ETOX Nor Flash process

- It generates adjustable voltages from 0.5V to 4.0V in 0.1V step with a ripple voltage of less than 80mV.

-

Charge-Pump positive voltage generator with LDO in-built on SMIC 65nm

- The present IP is a charge-pump and low dropout voltage generator, which is developed with SMIC 65nm ETOX Nor Flash process

- And it generates 4.5~6v high voltage (pump output) and 3V-4.2V trimmable voltages (LDO) based on the pump output for other blocks.

-

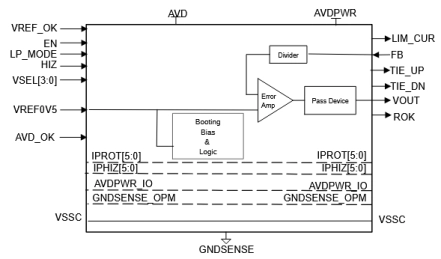

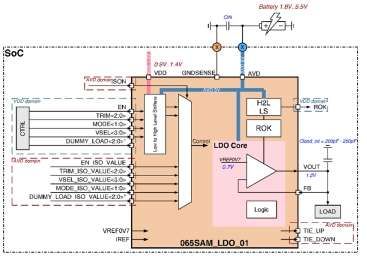

50 mA LDO voltage regulator (output voltage 0.9V/1.2V/1.34V) on Samsung 65nm

- 065SAM_LDO_01 is a low drop out voltage regulator designed to supply integrated circuits with stable and precise voltage.

- The LDO inputs voltage AVD from 1.8V to 5.5V and converts this voltage into a voltage VOUT 0.9V/1.2V/1.35V with 50mA load capacity.

- A Regulation OK (ROK) signal inform the system that LDO has completed its booting sequence and if its output is maintaining regulation for the current drawn by the load.

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 28nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 28nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;